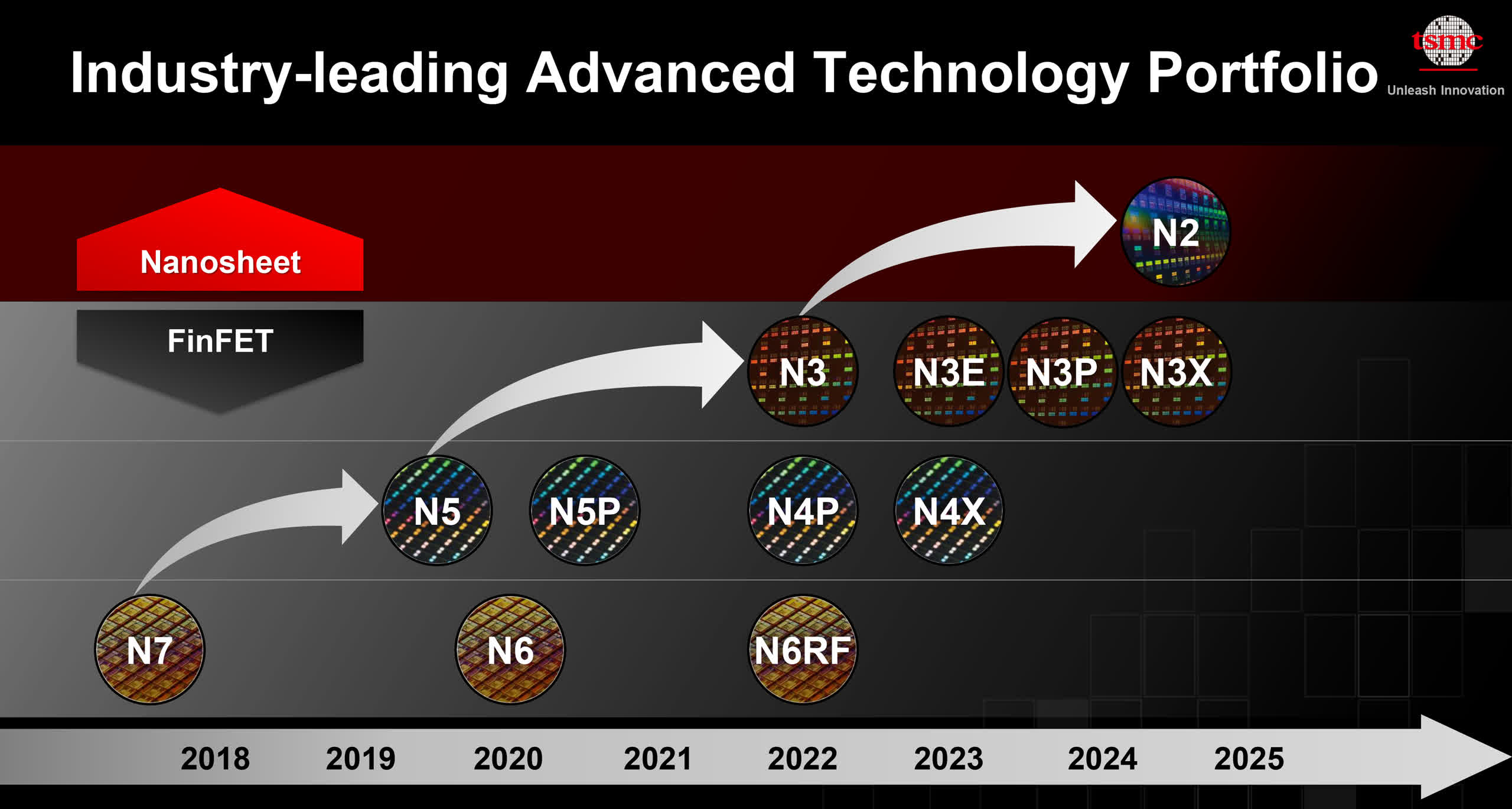

TSMC acaba de anunciar toda a sua linha de nós de classe de 3 nm que serão lançados nos próximos três anos. Sua nova tecnologia FinFlex dará aos designers de chips ainda mais flexibilidade para otimizar cada célula padrão para o consumo de energia, desempenho e densidade desejados.

A TSMC acaba de revelar toda a sua família N3 de nós de processo de 3 nm. Projetistas de chips como AMD, Apple, Nvidia e até mesmo Intel usarão esses nós nos próximos anos para fabricar seus chips de ponta.

A empresa taiwanesa tem um total de cinco nós de classe de 3nm diferentes. O N3 começará a fabricar em alto volume ainda este ano, com a expectativa de que os primeiros chips cheguem aos clientes no início do próximo ano. O N3E será lançado posteriormente com melhorias de desempenho e eficiência, rendimentos mais altos, mas densidade lógica ligeiramente reduzida.

Por volta de 2024, a TSMC lançará o N3P, que se concentra em melhorias de desempenho. O N3S, que não foi apresentado no roteiro da TSMC, foi apenas brevemente mencionado na conversa do vice-presidente sênior Kevin Zhang.

Finalmente, o N3X será lançado cerca de um ano depois e permitirá um desempenho extremamente alto em tensões mais altas, com eficiência e custos em segundo plano. Essa abordagem é semelhante ao processo N4X da classe de 5 nm que inicia a fabricação em volume no próximo ano.

Os nós N3 e N3E da TSMC também suportarão a nova tecnologia FinFlex da empresa . Atualmente, os designers de chips precisam escolher uma biblioteca para cada bloco dentro de um SoC. Com o FinFlex, eles não terão essa limitação e poderão misturar e combinar diferentes bibliotecas dentro de cada bloco.

Eles podem usar FinFETs 2-1 (porta dupla de aleta única) em algumas partes para reduzir o consumo de energia e o tamanho da matriz (custo) e optar por 3-2 FinFETs em outras áreas onde o desempenho máximo é primordial. Enquanto isso, 2-2 FinFETs fornecem um equilíbrio de tamanho, desempenho e consumo de energia.

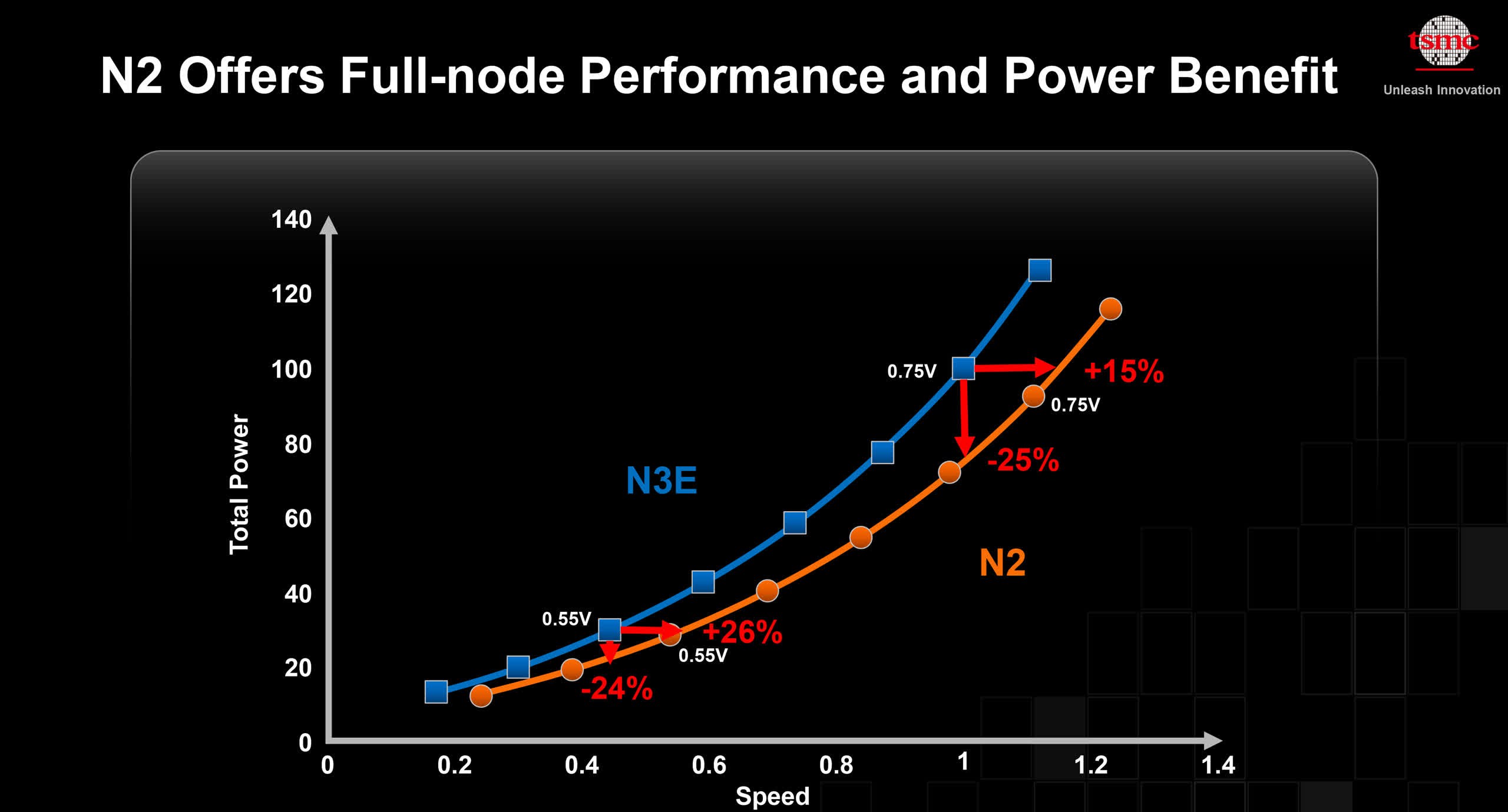

A TSMC também mencionou seu próximo nó de processo N2, que usará transistores de efeito de campo completos (GAAFETs), com planos de iniciar a fabricação em volume no segundo semestre de 2025.

Comparado ao N3E, ele consumirá 25 a 30% menos energia na mesma frequência e permitirá 10 a 15% mais desempenho com o mesmo consumo de energia e contagem de transistores. Enquanto isso, a densidade de chips aumentará em mais de 10%.