A Lei de Moore está em suporte de vida há algum tempo, mas ainda não está morta. Os fabricantes de chips estão queimando o petróleo da meia-noite para miniaturizar projetos de transistores, e uma equipe de pesquisadores na China criou o que se acredita ser o menor até agora. Já ouviu falar sobre o menor gate de transistor do mundo?

Por várias décadas, cientistas e engenheiros encolheram os transistores até o ponto em que seus menores recursos são compostos apenas por dezenas de átomos. Desde os primeiros circuitos integrados na década de 1950, a taxa de progresso na miniaturização de transistores seguiu a Lei de Moore, que previa que a densidade de componentes ativos em chips integrados dobraria a cada dois anos.

Como muitos de nossos leitores sabem, o progresso nessa direção diminuiu significativamente nos últimos anos. A principal razão é que estamos nos aproximando rapidamente dos limites físicos do que é possível com os materiais existentes e os processos de fabricação mais avançados que temos.

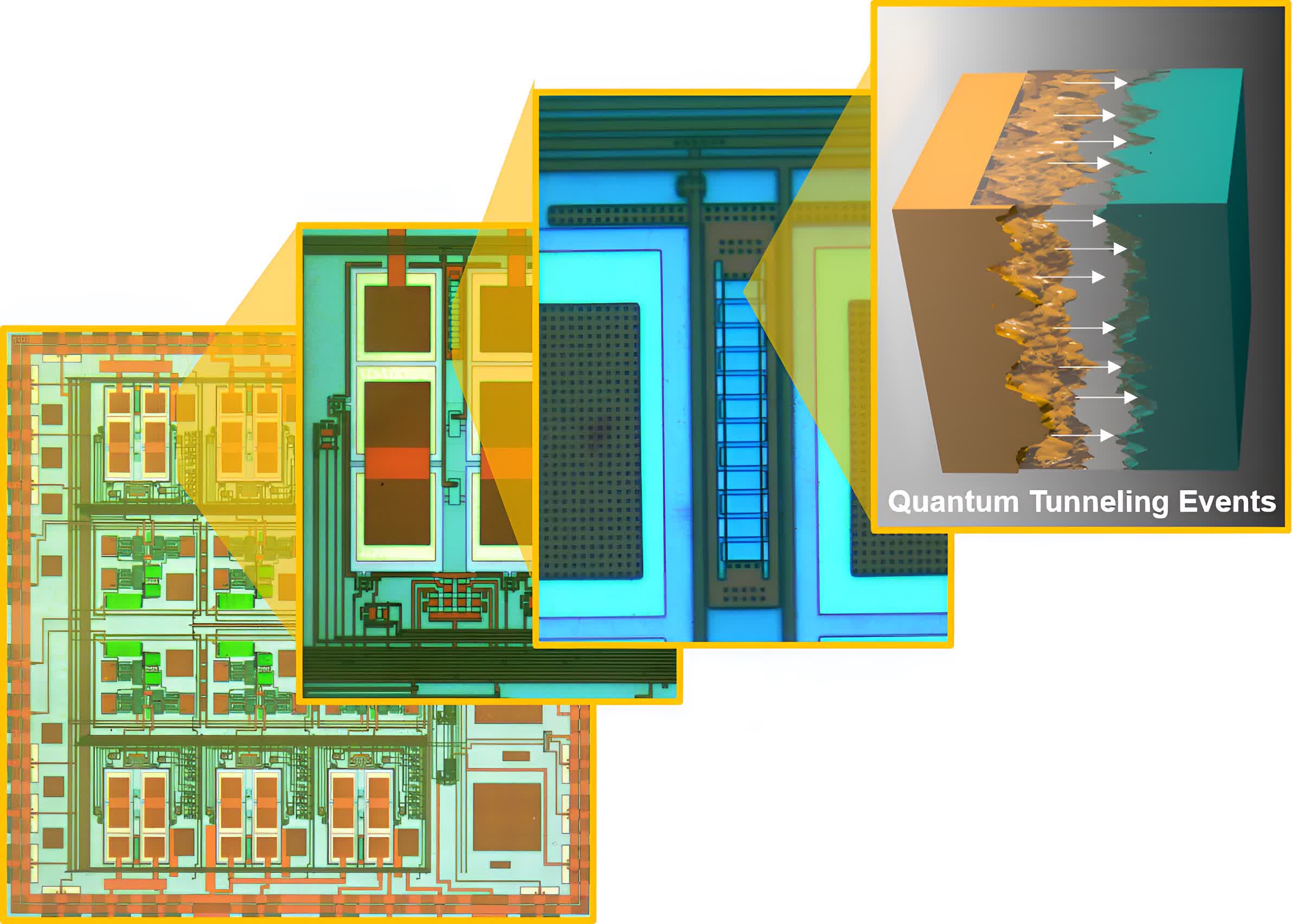

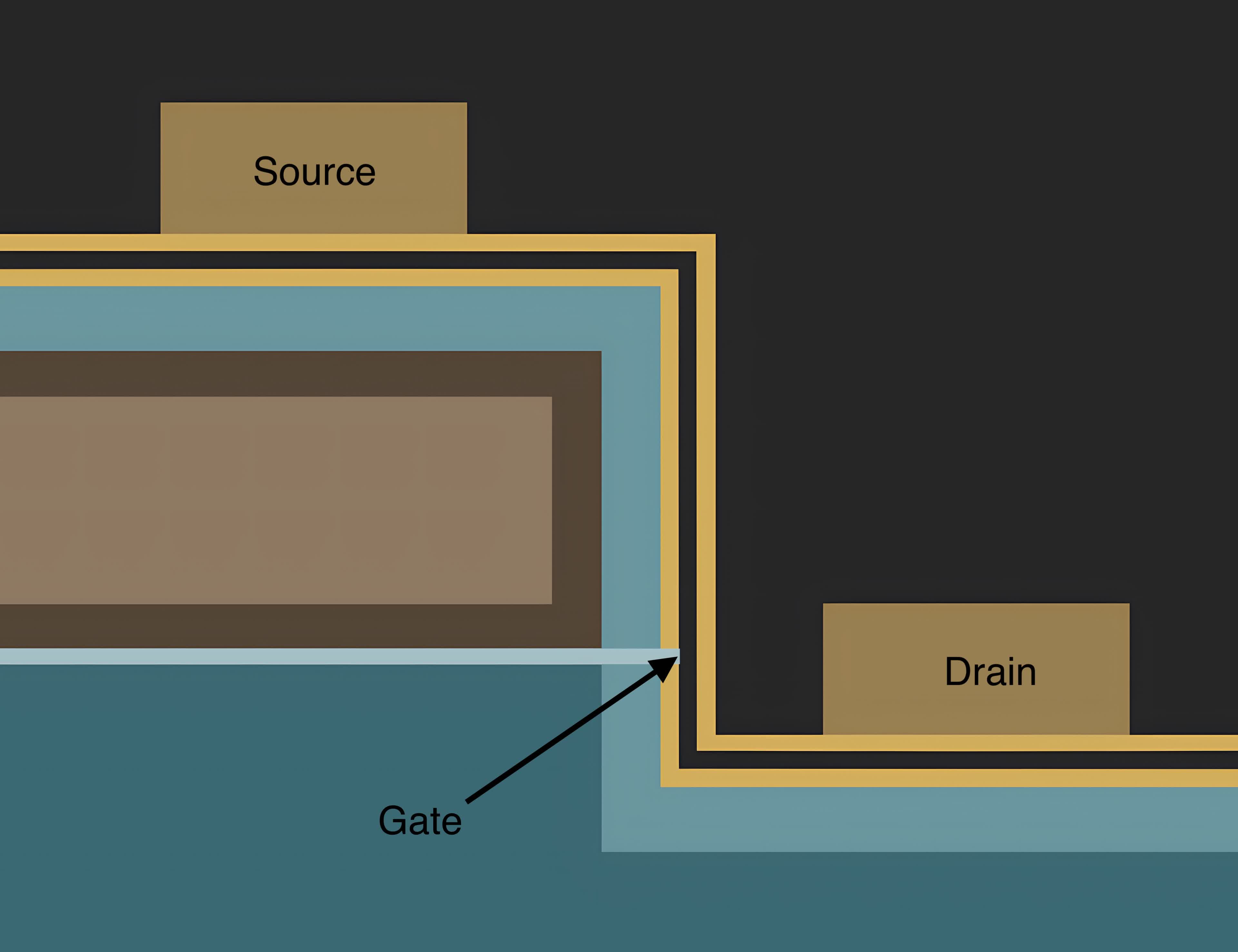

Mais especificamente, não podemos fazer portas de transistor – que controlam o fluxo de corrente da fonte para o dreno – muito menores que 5 nm por causa de algo chamado tunelamento quântico que os impede de funcionar como pretendido. Materiais como grafeno e nanotubos de carbono podem ser vitais para tornar os transistores ainda menores graças às suas propriedades físicas, mas levar um tempo para construir dispositivos funcionais.

O menor gate de transistor do mundo

Em um artigo divulgado esta semana, pesquisadores chineses explicam que criaram um transistor com o menor comprimento de porta já relatado. Este marco foi possível utilizando criativamente grafeno e dissulfeto de molibdênio e empilhando-os em uma estrutura de escada com dois degraus.

A estrutura do transistor de parede lateral: A parte azul escura é a base de dióxido de silício, a marrom é o alumínio coberto de óxido de alumínio, a fina tira azul clara é o grafeno, a amarela e a preta é o dissulfeto de molibdênio e abaixo dela , você tem o dióxido de háfnio.

No degrau mais alto, você tem a fonte e, no degrau mais baixo, o dreno. Ambos são feitos de uma liga de titânio-paládio separada pela superfície da escada, que é feita de uma única folha de um material semicondutor chamado dissulfeto de molibdênio, ele próprio repousando sobre uma camada de dióxido de háfnio que atua como isolante elétrico.

O interior do degrau mais alto é um sanduíche literal de alumínio coberto de óxido de alumínio, que repousa sobre uma folha de grafeno – uma única camada de átomos de carbono. O óxido de alumínio atua como um isolante elétrico, exceto por uma pequena abertura na parede vertical do degrau mais alto, onde a folha de grafeno pode entrar em contato com o dissulfeto de molibdênio. Toda a estrutura da escada repousa sobre uma espessa camada de dióxido de silício.

O truque para este projeto é que a borda da folha de grafeno é usada, o que significa que quando o portão está definido para o estado “ligado”, ele tem apenas 0,34 nm de largura – essencialmente a largura da própria camada de grafeno. Outra característica notável deste “transistor de parede lateral” é a sua fuga de corrente insignificante devido à maior resistência de estado desligado.

Os fabricantes podem aproveitar essa qualidade para aplicações de baixo consumo de energia. O melhor de tudo, seria relativamente fácil de fazer, embora muitos dos protótipos exigissem um pouco de tensão para acionar.

O pesquisador da Universidade de Tsinghua, Tian-Ling Ren, foi co-autor do estudo e disse que este poderia ser “o último nó da lei de Moore”. Ele também acredita que ir menor que 0,34 nm para o tamanho do portão é quase impossível.

Claro, os pesquisadores por trás do novo transistor só provaram que um transistor funcional poderia ser feito usando materiais finos de um átomo sem inventar um novo processo para o posicionamento preciso das camadas necessárias.

Construir de forma confiável bilhões desses transistores de parede lateral ainda é um sonho distante, mas é um passo crítico nessa direção, o que alimenta a esperança de dispositivos mais rápidos e com maior eficiência energética no futuro.

Enquanto isso, Samsung, Intel e TSMC estão trabalhando duro para tornar realidade os transistores gate-all-around (GAA-FET) e padronizar as interconexões para projetos de chiplet.