A Intel pode estar de olho em um novo design de transistor como a cavalaria macedônia para suas aspirações de fabricação abaixo de 2 nm. Uma patente online recentemente publicada parece apontar o caminho da Intel para manter a Lei de Moore viva por meio do que ela chama de “ transistores empilhados em forma de garfo ”. No entanto, a patente é confusa, como tendem a ser, e a Intel não reivindica melhorias no PPA (Power-Performance-Area).

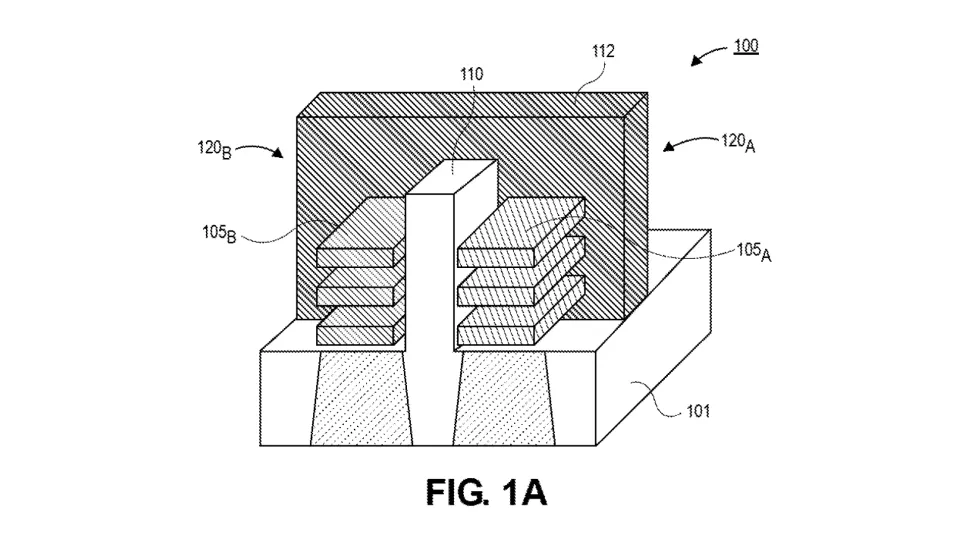

De acordo com o gigante azul, o novo design do transistor pode levar a uma arquitetura CMOS 3D empilhada verticalmente que permite maior contagem de transistores em comparação com os designs de tri-gate mais avançados de hoje. No entanto, as dificuldades de diminuir ainda mais os transistores tornaram-se tais que até mesmo a patente da Intel descreve as restrições como “esmagadoras” – o custo, o risco e a complexidade agora parecem superar os benefícios potenciais.

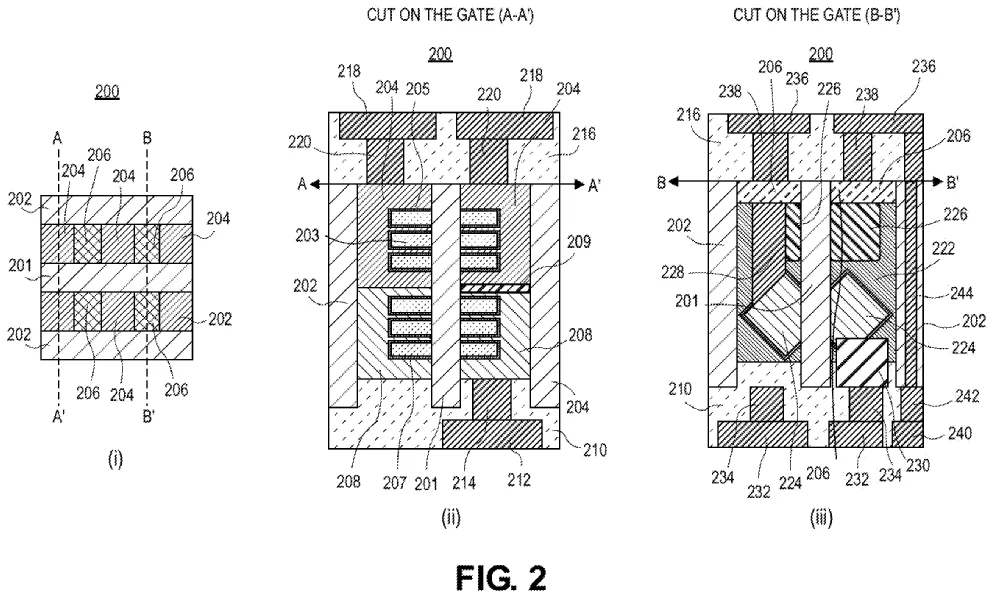

A patente da Intel descreve o uso de transistores de nanofitas emparelhados com um novo filme de germânio, fino como um átomo, que atua como uma parede dielétrica. A parede serve como uma separação física entre as camadas, atuando como um isolante entre a trincheira p-gate e a trincheira n-gate.

Ele é repetido através de cada uma das camadas de transistor empilhadas verticalmente, dependendo de quantos transistores estão sendo empilhados uns sobre os outros. Em termos práticos, isso permite espaços muito mais apertados entre os dispositivos P- e NMOS antes que suas funções sejam afetadas (em comparação com a distância que eles teriam que ser para o mesmo efeito sem a parede), o que significa que a Intel pode encaixar mais deles em uma área menor. Como resultado, a Lei de Moore apenas tomou outro fôlego – ainda que irregular.

A Intel já havia começado a explorar a tecnologia já em 2019 – a empresa a apresentou em seu evento Electronic Devices Meeting (IEDM). No entanto, nem nesta patente nem lá podemos encontrar dados concretos sobre algumas “estimativas rígidas” sobre como a tecnologia de forksheet pode melhorar a densidade, o desempenho e a eficiência de energia do transistor.

Felizmente, a Intel não é a primeira empresa a fazer referência a esse método de fabricação. O Imec, um grupo de pesquisa com sede na Bélgica, anunciou o desenvolvimento dos primeiros resultados de simulação de célula padrão para “dispositivos de forksheet” em 2019 – e sim, esses dispositivos de forksheet são a base da patente da Intel. Portanto, não é surpresa que duas instituições tenham laços próximos e duradouros em nanoeletrônica.

Transistores empilhados

De acordo com os primeiros resultados de simulação de célula padrão do Imec , quando aplicada a um nó de tecnologia de 2 nm, a tecnologia pode fornecer melhorias significativas na densidade do transistor em comparação com as abordagens tradicionais de nanofolhas. Estamos olhando para um aumento de velocidade de 10% ou uma melhoria de eficiência energética de 24% em velocidades constantes, combinado com uma “redução de mais de 20% na área da célula”. Além disso, a área de memória de acesso aleatório estático (SRAM) (que geralmente compõe o cache de uma CPU e é um dos contribuintes mais significativos para a área de matriz) recebe uma redução impressionante de 30%.

Compare isso com as melhorias anunciadas da TSMC de seu nó de 3 nm em comparação com 5 nm: um ganho de desempenho de 10 a 15% (na mesma potência e contagem de transistores), até 30% de redução de energia (nos mesmos clocks e complexidade), até 70% ganho de densidade lógica (adequado para núcleos) e um ganho de densidade SRAM de até 20%.

Devemos lembrar que nem todas as patentes se transformam em produtos ou tecnologias de fabricação reais – às vezes são maneiras de proteger um investimento potencial ou provisório ou locais de pesquisa ou até mesmo queimar metaforicamente os avanços dos concorrentes nesse terreno. No entanto, a pesquisa do Imec de 2019 já apresentava melhorias possíveis impressionantes para um nó sub-2nm, especialmente quando se considera que está dentro da resolução exata de gravação, mas com uma arquitetura de transistor diferente. Então é salto – sem salto de nó.Propaganda

A Intel agora teve tempo para obter muito mais pesquisas, e agora sabemos que a pesquisa sobre transistores empilhados continuou até pelo menos junho de 2020. E também sabemos que o planejamento e a pesquisa de fabricação de semicondutores são incrivelmente longos. O CEO da Intel, Pat Gelsinger, mencionou pela primeira vez a tecnologia de 10 nm – agora Intel 7 – em 2008, quando ainda atuava como CTO, alegando que viu “um caminho claro” para isso. Essa maneira clara só se manifestou verdadeiramente no Alder Lake deste ano, que mostra os requisitos de capital da fabricação de semicondutores de ponta. Intel 7 pode ter chegado tarde, mas Alder Lake bate recordes mundiais de overclock.

Não está claro se a Intel optará por uma arquitetura de forksheet empilhada em um processo de 2 nm ou se deseja colher seus benefícios de design mais cedo.

Mas a Intel registrou o pedido de patente, o que significa que o design tem algum mérito. Infelizmente, parece que a empresa sabe mais do que nós sobre a viabilidade da tecnologia.