Se você tivesse me dito há apenas alguns anos que a Arm criaria designs que poderiam competir em computação de alto desempenho (HPC) e outros aplicativos superexigentes, provavelmente não teria acreditado em você. Afinal, o Arm é conhecido principalmente pela eficiência de energia de seus designs – portanto, é um enorme sucesso em smartphones e outros dispositivos alimentados por bateria.

Claro, o desempenho em chips de smartphones baseados em Arm, como a série A da Apple para iPhones, a linha Snapdragon da Qualcomm para dispositivos Android e outros tem melhorado dramaticamente nos últimos anos, mas há uma grande lacuna entre smartphones e HPC.

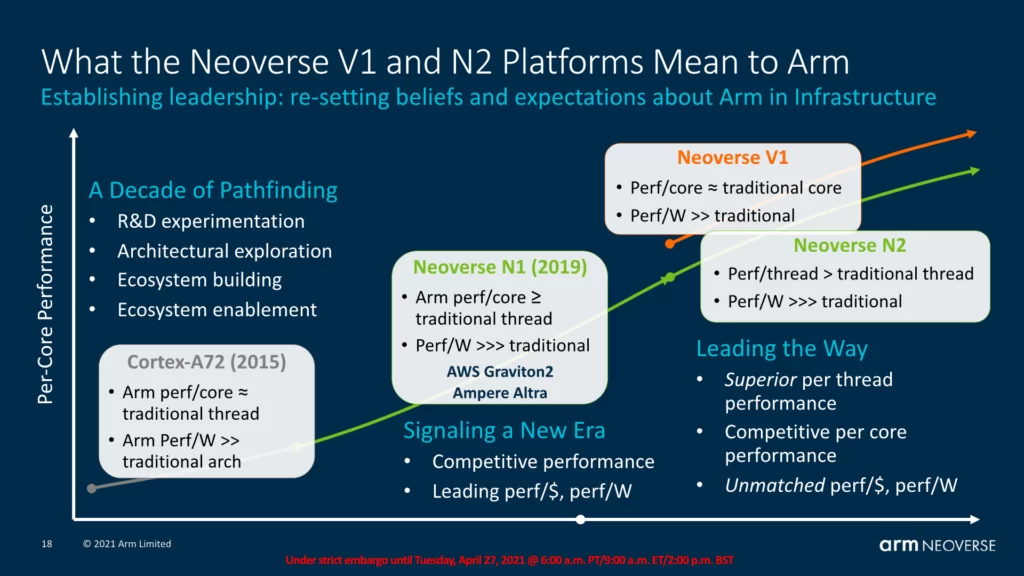

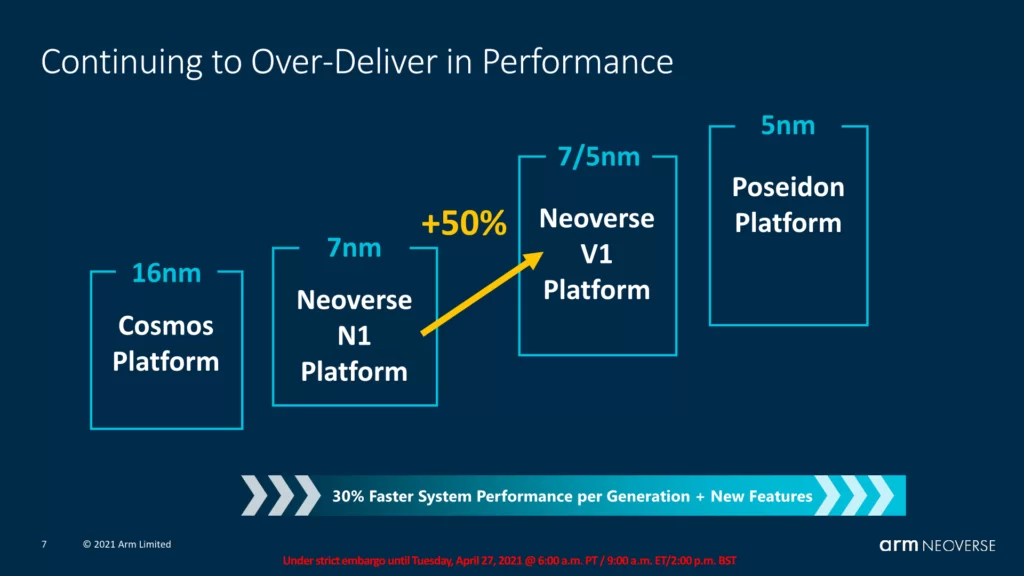

No entanto, as coisas começaram a mudar quando a Arm revelou sua plataforma Neoverse N1 para aplicativos focados em nuvem e datacenter em 2019. Com a estreia do design da CPU N1, a empresa sinalizou fortemente para seus parceiros e para o mundo da computação em geral que levava a sério entrando no mercado de servidores.

O esforço conquistou uma série de vitórias de design notáveis, incluindo o processador Graviton da AWS , que a Amazon está usando agora – junto com seu sucessor, o Graviton 2 – para uma gama cada vez mais ampla de diferentes cargas de trabalho. Ainda assim, muitos dos primeiros esforços e sucessos se concentraram na eficiência de energia dos designs baseados em Arm para data centers em nuvem – um fator importante, mas muitas vezes esquecido nesses ambientes.

No início desta semana, no entanto, a Arm estendeu ainda mais sua família Neoverse com o lançamento da plataforma V1, que é voltada para aplicativos de alto desempenho. A empresa diz que o V1 oferece uma melhoria impressionante de 50% nas instruções por clock (IPC), um aumento de 2x no desempenho do vetor e um salto de 4x no desempenho do aprendizado de máquina em relação ao N1 original.

Parte da maneira como o Arm está alcançando essas novas métricas de desempenho é através da adição de Extensões de Vetor Escaláveis (SVE), que essencialmente permite instruções personalizadas que podem lidar com blocos de dados de qualquer comprimento a serem adicionados aos designs de CPU. Mais importante, ele permite que o código escrito para um tipo de comprimento de vetor seja capaz de ser executado em hardware que pode ter um comprimento de vetor diferente, melhorando assim a flexibilidade e a portabilidade do software envolvido.

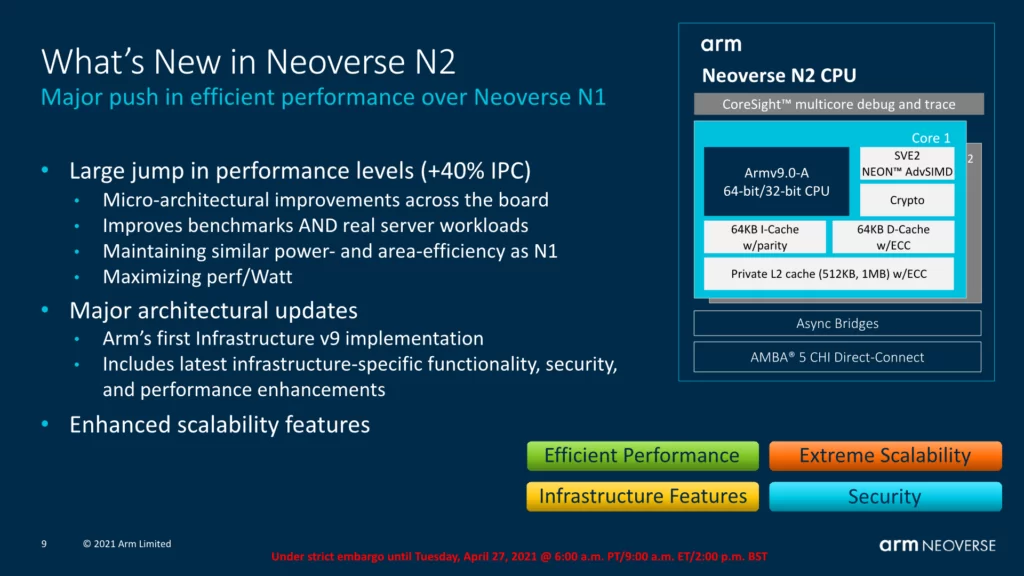

Neoverse N2 – a primeira CPU de infraestrutura Armv9 da Arm

Além do V1, a Arm também revelou o N2 de segunda geração , que é baseado no mesmo design com foco em desempenho / watt do N1 original, mas com uma grande variedade de aprimoramentos na microarquitetura. Notavelmente, o N2 também é o primeiro design de CPU da Arm a alavancar sua arquitetura V9 (consulte “Arm Lays Out Vision for Next Decade of Chips” para mais). Por causa dessa nova arquitetura subjacente, ele adiciona suporte para SVE2, a segunda geração de Extensões de Vetor Escaláveis da Arm.

Tudo isso se traduz em uma alegada melhora de 40% no desempenho em relação ao N1 original, enquanto mantém o menor consumo de energia e térmicas do N1. Tão importante quanto, ele fornece a prova da intenção da Arm de continuar desenvolvendo e aprimorando sua gama de designs de chips com foco no servidor. Com as duas novas arquiteturas de chip, empresas como a Ampere e outros parceiros da Arm podem escolher criar SoCs focados em datacenter que são mais concentrados no desempenho (mas consomem mais energia) ou são mais concentrados na eficiência energética, enquanto ainda fornecem velocidades aprimoradas.

Tudo isso se traduz em uma alegada melhora de 40% no desempenho em relação ao N1 original, enquanto mantém o menor consumo de energia e térmicas do N1.

Uma parte crítica, mas fácil de ignorar, dos anúncios da Arm é a estreia de sua CoreLink CMN-700 Coherent Mesh Network para uso em conjunto com essas novas CPUs. Construído para permitir designs mais flexíveis no estilo de chips, o CMN 700 fornece conexões de dados de alta velocidade críticas entre componentes em um SoC.

Por exemplo, fabricantes de semicondutores que desejam ter mais opções para conectar aceleradores personalizados, bem como formas avançadas de memória e armazenamento, podem aproveitar a tecnologia de rede em malha da Arm para fazer isso. O CoreLink CMN-700 agora inclui suporte para os padrões CXL (Compute Express Link) e CCIX (Cache Coherent Interconnect for Accelerators), além de fornecer gateways que podem conectar esses barramentos ao barramento de interconexão de CPU AMBA 5 da própria Arm. O resultado final é uma gama significativamente mais flexível de opções de design que permitirão aos projetistas de chips reunir peças especializadas com mais facilidade usando blocos de funcionalidade semelhantes a blocos Lego.

Na prática, esses recursos permitem que empresas como a Marvell usem essas novas tecnologias Arm em produtos como suas DPUs (unidades de processamento de dados) de última geração para uso em 5G e outros aplicativos de rede de alta velocidade, bem como Oracle para sua infraestrutura de nuvem.

Devido à natureza de seu processo de design e ao papel que desempenham na indústria, muitas dessas inovações da Arm não estarão em aplicações do mundo real até 2022 e além. Ainda assim, é bom ver a empresa expandindo os limites da computação em nuvem e desempenho de computação de ponta além de seus objetivos originais e será interessante ver onde e até onde seus parceiros levam esses recursos.