A AMD em seu evento do Financial Analyst Day de 2020 apresentou sua próxima arquitetura de acelerador de computação baseada em GPU CDNA e CDNA2. O CDNA complementará a arquitetura RDNA orientada a gráficos da empresa. Enquanto o RDNA alimenta os produtos gráficos empresariais e para clientes Radeon Pro e Radeon RX da empresa, o CDNA aciona aceleradores de computação como o Radeon Instinct etc. A AMD está tendo que forçar seu IP gráfico para RDNA e CDNA devido ao que descreveu como baseado no mercado diferenciação do produto.

Os datacenters e HPCs que usam aceleradores Radeon Instinct não têm utilidade para os recursos reais de renderização gráfica. E assim, no nível do silício, a AMD está removendo o hardware gráfico raster, os mecanismos de exibição e multimídia e outros componentes associados que ocupam quantidades significativas de área da matriz. Em seu lugar, a AMD está adicionando hardware de computação de tensor de função fixa, semelhante aos núcleos de tensor em determinadas GPUs NVIDIA.

A AMD também falou sobre fornecer às GPUs de computação interfaces de memória avançadas HBM2e, interconexão Infinity Fabric além de PCIe etc. Os aceleradores de computação da geração atual da empresa são baseados nas arquiteturas “Vega” datadas e são essencialmente reconfigurados GPUs “Vega 20” que não possuem hardware tensor.

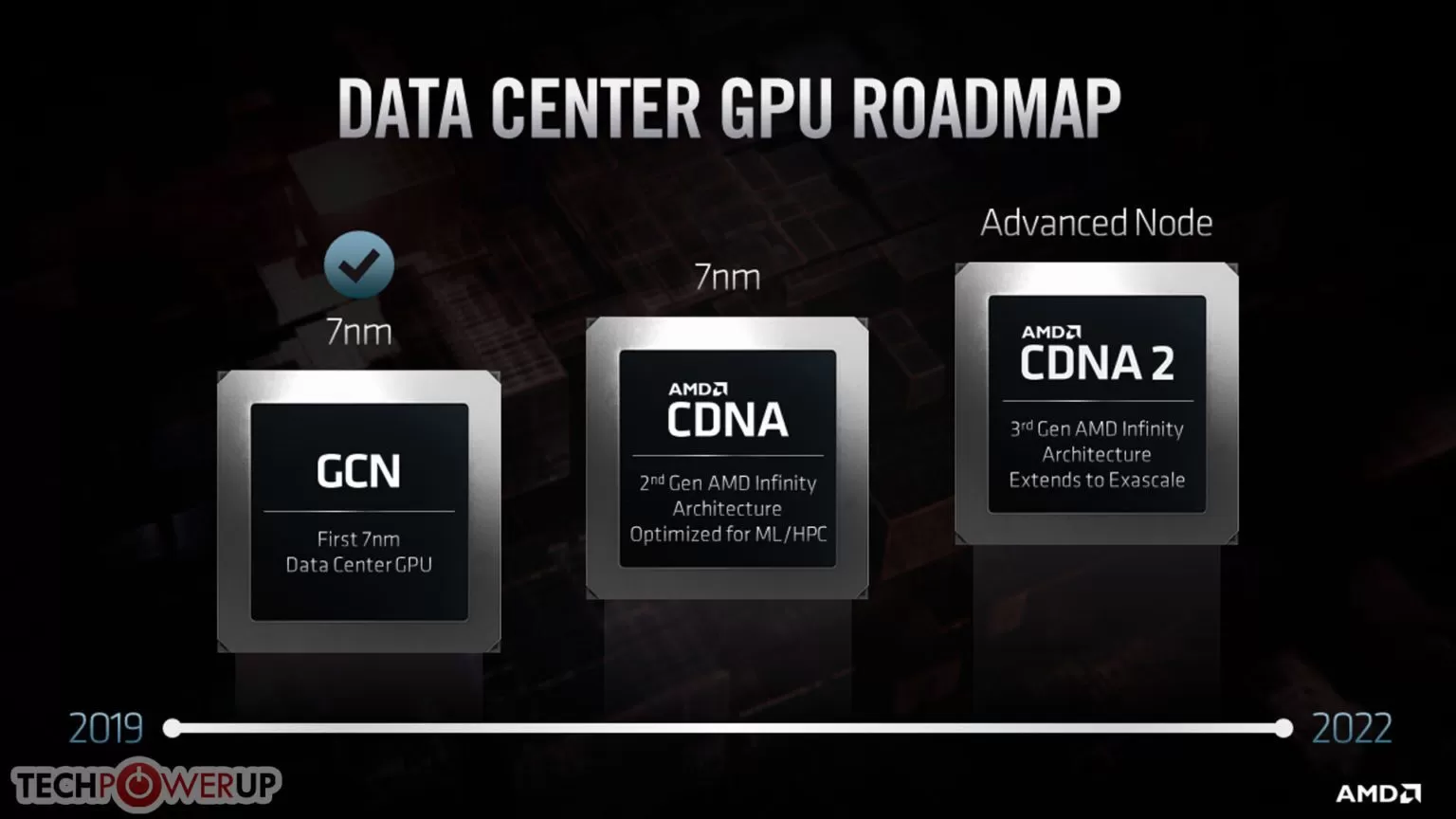

No final deste ano, a empresa apresentará sua primeira GPU CDNA baseada no processo “7 nm”, unidade de computação rival da IPC com RDNA e hardware tensor que acelera a construção e o treinamento do AI DNN.

Entre 2021 e 2022, a AMD apresentará sua arquitetura CDNA2 atualizada com base em um “processo avançado” que a AMD ainda não finalizou. A empresa está bastante confiante de que a microarquitetura da CPU “Zen4” irá alavancar 5 nm, mas não foi claro o mesmo para o CDNA2 (ambos são lançados ao mesmo tempo). Além de aumentar o IPC, as unidades de computação e outras coisas, o foco do design no CDNA2 será a hiperescalabilidade (a capacidade de escalar GPUs em vastos conjuntos de memória que abrangem milhares de nós). A AMD utilizará sua interconexão de terceira geração Infinity Fabric e memória unificada coerente em cache para fazer isso.

Assim como o Compute eXpress Link (CXL) da Intel e o PCI-Express gen 5.0, o Infinity Fabric 3.0 oferece suporte a conjuntos de memórias compartilhadas entre CPUs e GPUs, possibilitando escalabilidade do tipo exigido por supercomputadores de escala exótica, como o próximo “El Capitan” do US-DoE e “Frontier.” A memória unificada coerente do cache reduz transferências desnecessárias de dados entre a memória DRAM anexada à CPU e o HBM anexado à GPU. Os núcleos da CPU poderão processar diretamente vários estágios de computação serial de uma operação de computação da GPU conversando diretamente com o HBM conectado à GPU e não puxando dados para sua própria memória principal. Isso reduz bastante o estresse de E/S. “El Capitan” é um supercomputador “all-AMD” com até 2 exaflops (2.000 petaflops ou 2 milhões de TFLOPs). Combina AMD EPYC “Genoa”

Ah, o lado do software, a mais recente infraestrutura de software de código aberto ROCm da AMD reunirá CDNA e CPUs, fornecendo um modelo de programação unificado que rivaliza com o OneAPI da Intel e o NVIDIA CUDA. Uma API independente de plataforma compatível com qualquer GPU será combinada com uma camada de tradução CUDA para HIP.

Quer saber mais sobre esta e outras tecnologias visite nosso setor especializado em hardware e tecnologia.