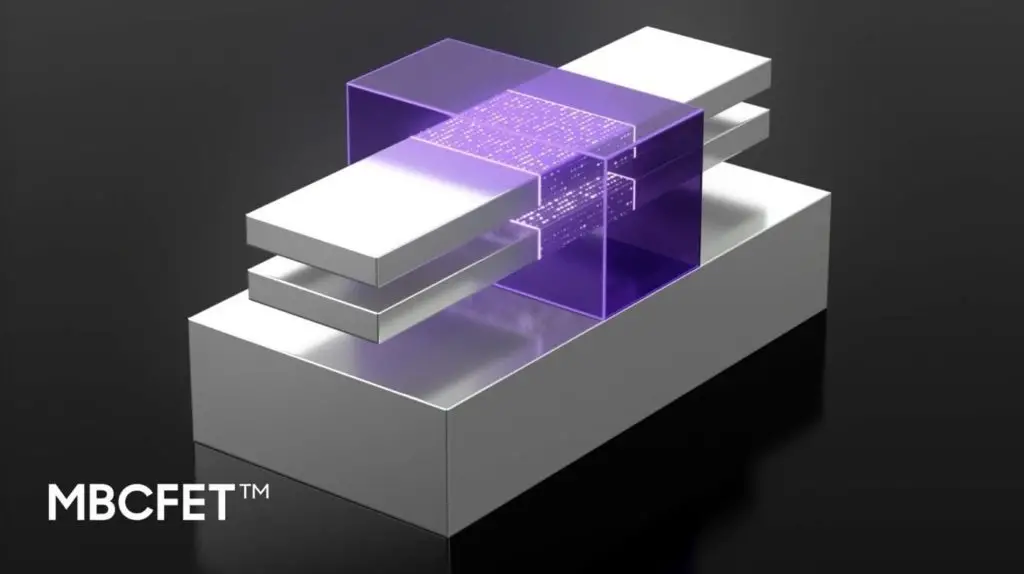

A Samsung está determinada em seus planos de entregar o processo de fabricação de silício de 3 nm no ano de 2022 e, com ele, haverá algumas melhorias importantes na tecnologia de transistor que conhecemos. Já mencionamos que a Samsung está trabalhando na tecnologia Gate-All-Around FET que trará um controle muito melhor do canal do transistor, evitando vazamentos em nós menores.

No entanto, hoje a Samsung adicionou mais alguns detalhes sobre sua futura tecnologia FET Multi Bridge Channel para um processo de fabricação de 3 nm, chamado simplesmente de MBCFET. Graças ao relatório da Hardwareluxx, temos mais detalhes sobre a tecnologia MBCFET e suas características.

Em primeiro lugar, vale a pena notar que o MCBFET faz parte dos GAAFETs, o que significa que o GAAFET não é um produto, mas uma classe de muitos com base em seus conceitos. Quanto ao desempenho do MCBFET, a Samsung diz que a tecnologia consumirá 50% menos energia e, ao mesmo tempo, terá 30% mais desempenho.

Além disso também haverá um grande ganho de densidade, onde a Samsung prevê que haverá cerca de 45% menos espaço de silício ocupado por um transistor. A comparação é feita com um processo não especificado de 7 nm, possivelmente o processo da Samsung que usa FinFETs.

A tecnologia adotada permite o empilhamento de transistores uns sobre os outros, o que faz com que ele use inerentemente menos espaço em comparação com o FinFET comum usado atualmente. Sendo que os transistores MCBFET GAA tornam sua largura de transistor flexível, isso significa que o transistor empilhado em geral pode ser tão largo quanto um projetista precisa.

Imaginar processadores ou memorias de 3 nm pode ser algo bem complexo, já que permite a redução da escala de construção ou um aumento significativo no poder de processamento do chip.

Saiba mais sobre esses e outros projetos em nosso setor especializado em hardware.