Ficou na duvida entre AMD Navi ou Nvidia Turing? Depois de pesquisar muito e analisar finalmente, você jogou fora seu dinheiro e saiu com uma das mais recentes placas de vídeo da AMD ou Nvidia. Dentro deles, encontra-se um grande processador gráfico, embalado com bilhões de transistores, todos funcionando em velocidades de clock impensáveis uma década atrás.

Você está muito feliz com sua compra e os jogos nunca pareceram nem foram melhor jogados. Mas você deve estar se perguntando o que exatamente está alimentando seu novo Radeon RX 5700 e como ele é diferente do chip em uma GeForce RTX .

Bem-vindo à nossa comparação de arquitetura e recursos das mais novas GPUs da AMD e Nvidia: Navi vs Turing.

Anatomia de uma GPU moderna

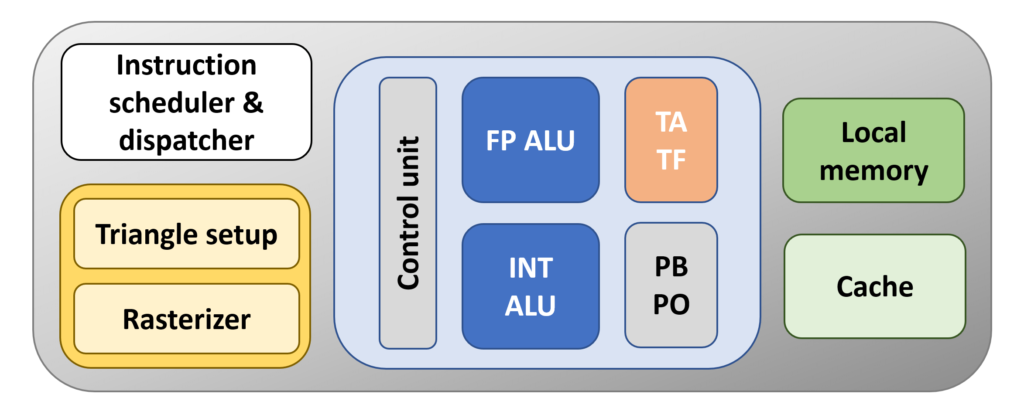

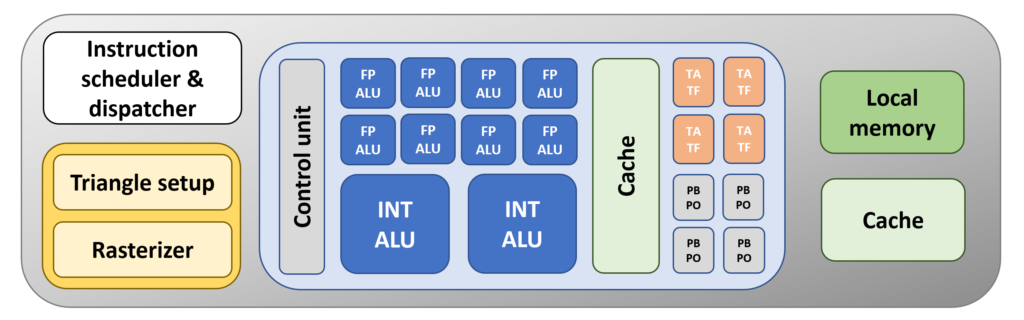

Antes de começarmos nossa análise das estruturas e sistemas gerais do chip, vamos dar uma olhada no formato básico que todas as GPUs modernas seguem. Na maior parte, esses processadores são apenas calculadoras de ponto flutuante (FP); em outras palavras, eles fazem operações matemáticas em valores decimais / fracionários.

Portanto, no mínimo, uma GPU precisa ter uma unidade lógica dedicada a essas tarefas e geralmente são chamadas de FP ALUs ( unidades lógicas aritméticas de ponto flutuante ) ou FPUs, abreviadamente. Nem todos os cálculos que as GPUs fazem são sobre valores de dados FP, então também haverá uma ALU para operações matemáticas de número inteiro ( inteiros ) ou pode até ser a mesma unidade, que apenas lida com os dois tipos de dados.

Agora, essas unidades lógicas vão precisar de algo para organizá-las, decodificando e emitindo instruções para mantê-las ocupadas, e isso será na forma de pelo menos um grupo dedicado de unidades lógicas. Ao contrário das ALUs, eles não são programáveis pelo usuário final; em vez disso, o fornecedor do hardware garantirá que esse processo seja totalmente gerenciado pela GPU e seus drivers.

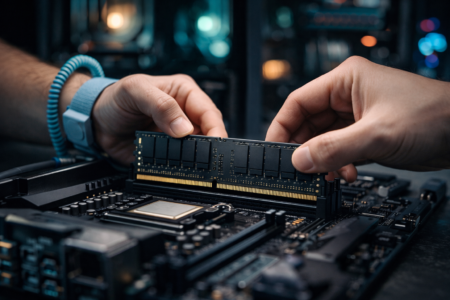

Para armazenar essas instruções e os dados que precisam ser processados, deve haver algum tipo de estrutura de memória também. Em seu nível mais simples, ele terá duas formas: cache e um ponto de memória local. O primeiro será incorporado à própria GPU e será SRAM.

Esse tipo de memória é rápido, mas ocupa uma quantidade relativamente grande do layout do processador. A memória local será DRAM , que é um pouco mais lenta que a SRAM e normalmente não será colocada na própria GPU. A maioria das placas de vídeo que vemos hoje tem memória local na forma de módulos DRAM GDDR .

Finalmente, a renderização de gráficos 3D envolve tarefas de conjunto adicionais, como formar triângulos a partir de vértices, rasterizar um quadro 3D, amostrar e mesclar texturas e assim por diante. Como as unidades de instrução e controle, essas são funções fixas por natureza. O que eles fazem e como operam é completamente transparente para os usuários programando e usando a GPU.

Vamos juntar isso e fazer uma GPU:

O bloco laranja é a unidade que lida com as texturas usando as chamadas unidades de mapeamento de textura (TMUs) – TA é a unidade de endereçamento de textura – ele cria os locais de memória para o cache e a memória local usarem – e TF é a unidade de busca de textura que coleta valores de textura da memória e os mistura.

Hoje em dia, as TMUs são praticamente as mesmas em todos os fornecedores, no sentido de que podem abordar, amostrar e combinar diversos valores de textura por ciclo de clock da GPU.

O bloco abaixo dele grava os valores de cor para os pixels no quadro, bem como faz uma amostragem deles (PO) e mescla-os (PB); este bloco também executa operações que são usadas quando o anti-aliasing é empregado.

O nome para este bloco é unidade de saída de renderização ou backend de renderização (ROP / RB para abreviar). Como o TMU, eles são bastante padronizados agora, com cada um manipulando confortavelmente vários pixels por ciclo de clock.

Nossa GPU básica seria péssima, mesmo para os padrões de 13 anos atrás. Por quê?

Há apenas um FPU, TMU e ROP. Os processadores gráficos em 2006, como o GeForce 8800 GTX da Nvidia, tinham 128, 32 e 24 deles, respectivamente. Então, vamos começar a fazer algo sobre isso …

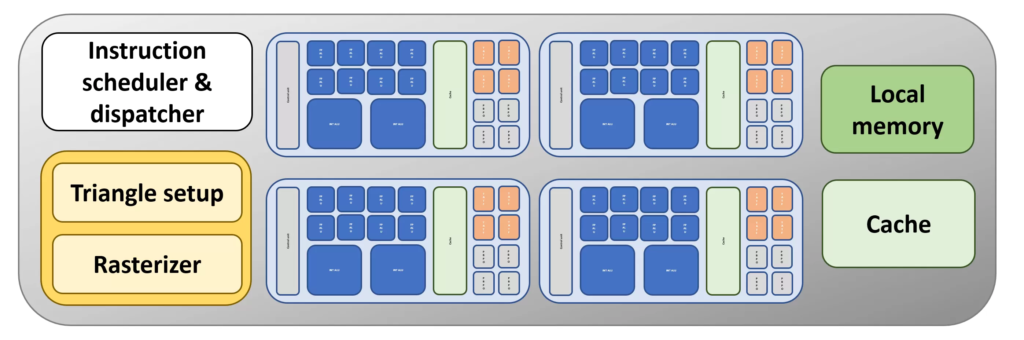

Como qualquer bom fabricante de processadores, atualizamos nossa GPU adicionando mais algumas unidades. Isso significa que o chip será capaz de processar mais instruções simultaneamente.

Para ajudar com isso, também adicionamos um pouco mais de cache, mas desta vez, bem ao lado das unidades lógicas. Quanto mais próximo o cache estiver de uma estrutura de calculadora, mais rápido ele poderá iniciar as operações fornecidas a ele.

O problema com nosso novo design é que ainda há apenas uma unidade de controle lidando com nossas ALUs extras. Seria melhor se tivéssemos mais blocos de unidades, todos gerenciados por seus próprios controladores separados, pois isso significaria que poderíamos ter operações muito diferentes ocorrendo ao mesmo tempo.

Agora é mais parecido com isso! Blocos ALU separados, embalados com seus próprios TMUs e ROPs e suportados por fatias dedicadas de cache saboroso e rápido. Ainda há apenas um de tudo o mais, mas a estrutura básica não está a um milhão de milhas de distância do processador gráfico que vemos nos PCs e consoles hoje.

AMD Navi ou Nvidia Turing: GPUs Godzilla

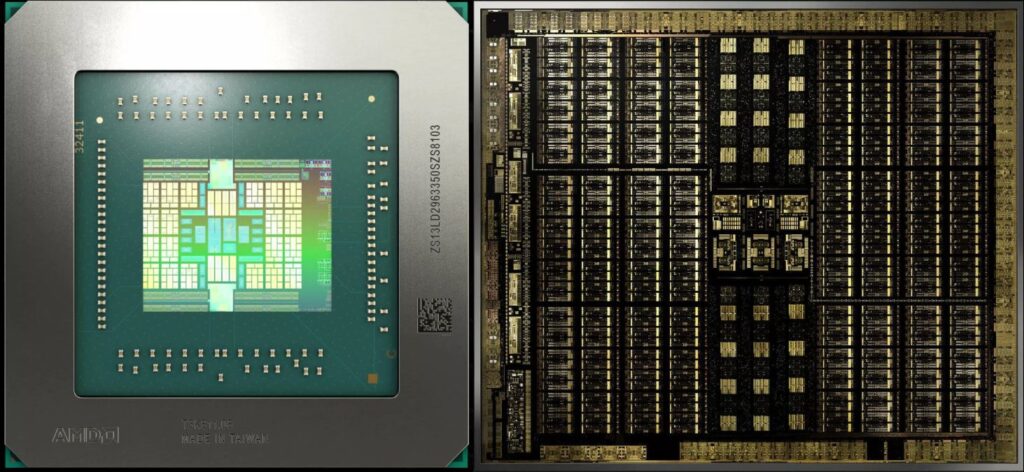

Agora que descrevemos o layout básico de um chip gráfico, vamos começar nossa comparação Navi vs. Turing com algumas imagens dos chips reais, embora um pouco ampliadas e processadas para destacar as várias estruturas.

À esquerda está o mais novo processador da AMD. O design geral do chip é chamado de Navi (algumas pessoas o chamam de Navi 10) e a arquitetura gráfica é chamada de RDNA. Próximo a ele, à direita, está o processador TU102 de tamanho normal da Nvidia, ostentando a mais recente arquitetura de Turing. É importante notar que essas imagens não estão em escala: a matriz Navi tem uma área de 251 mm2, enquanto a TU102 tem 752 mm2. O processador Nvidia é grande, mas não é 8 vezes maior do que a oferta da AMD!

Ambos estão embalando um número gigantesco de transistores (10,3 contra 18,6 bilhões), mas o TU102 tem uma média de ~ 25 milhões de transistores por mm quadrado em comparação com os 41 milhões de Navi por mm quadrado.

Isso porque, embora ambos os chips sejam fabricados pela TSMC, eles são fabricados em nós de processo diferentes: o Turing da Nvidia está na linha de fabricação de 12 nm, enquanto o Navi da AMD é fabricado no nó de 7 nm mais recente.

Apenas olhar as imagens das matrizes não nos diz muito sobre as arquiteturas, então vamos dar uma olhada nos diagramas de blocos de GPU produzidos por ambas as empresas.

Os diagramas não pretendem ser uma representação 100% realista dos layouts reais, mas se você girá-los em 90 graus, os vários blocos e a faixa central que são aparentes em ambos podem ser identificados. Para começar, podemos ver que as duas GPUs têm uma estrutura geral como a nossa (embora com mais de tudo!).

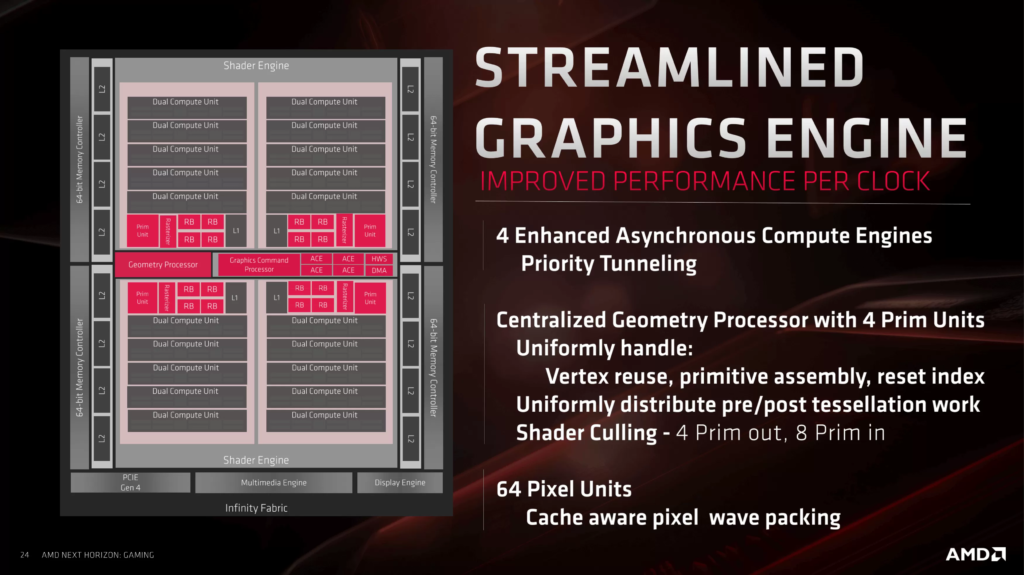

Ambos os projetos seguem uma abordagem faseada à forma como tudo é organizado e agrupado – tomando Navi para começar, a GPU é construído a partir de 2 blocos que a AMD chama motores de sombreamento (SES), que são cada dividida em mais 2 blocos chamados Asynchronous Engines Compute ( ACEs). Cada um deles compreende 5 blocos, intitulados Workgroup Processors (WGPs), que por sua vez consistem em 2 unidades computacionais (UCs).

Para o projeto de Turing, os nomes e números são diferentes, mas a hierarquia é muito semelhante: 6 Graphics Processing Clusters (GPCs), cada um com 6 Texture Processing Clusters (TPCs), com cada um formado por 2 Streaming Multiprocessor (SM) blocos.

Se você imaginar um processador gráfico como uma grande fábrica, onde diferentes seções fabricam diferentes produtos, usando as mesmas matérias-primas, então essa organização começa a fazer sentido.

O CEO da fábrica envia todos os detalhes operacionais para a empresa, onde eles são divididos em várias tarefas e cargas de trabalho. Por ter várias seções independentes na fábrica, a eficiência da força de trabalho é aprimorada. Para GPUs, não é diferente e a palavra-chave mágica aqui é agendamento .

AMD Navi ou Nvidia Turing: programação e despacho

Quando demos uma olhada em como funciona a renderização de jogos 3D, vimos que um processador gráfico nada mais é do que uma calculadora super rápida, realizando uma série de operações matemáticas em milhões de dados. Navi e Turing são classificados como processadores Single Instruction Multiple Data (SIMD), embora uma descrição melhor seria Single Instruction Multiple Threads (SIMT).

Um jogo 3D moderno gera centenas de threads, às vezes milhares, pois o número de vértices e pixels a serem processados é enorme. Para garantir que tudo seja feito em apenas alguns microssegundos, é importante ter tantas unidades lógicas tão ocupadas quanto possível, sem que tudo pare porque os dados necessários não estão no lugar certo ou não há espaço de recursos suficiente para trabalhar dentro.

Quando demos uma olhada em como funciona a renderização de jogos 3D, vimos que um processador gráfico nada mais é do que uma calculadora super rápida, realizando uma série de operações matemáticas em milhões de dados. Navi e Turing são classificados como processadores Single Instruction Multiple Data (SIMD), embora uma descrição melhor seria Single Instruction Multiple Threads (SIMT).

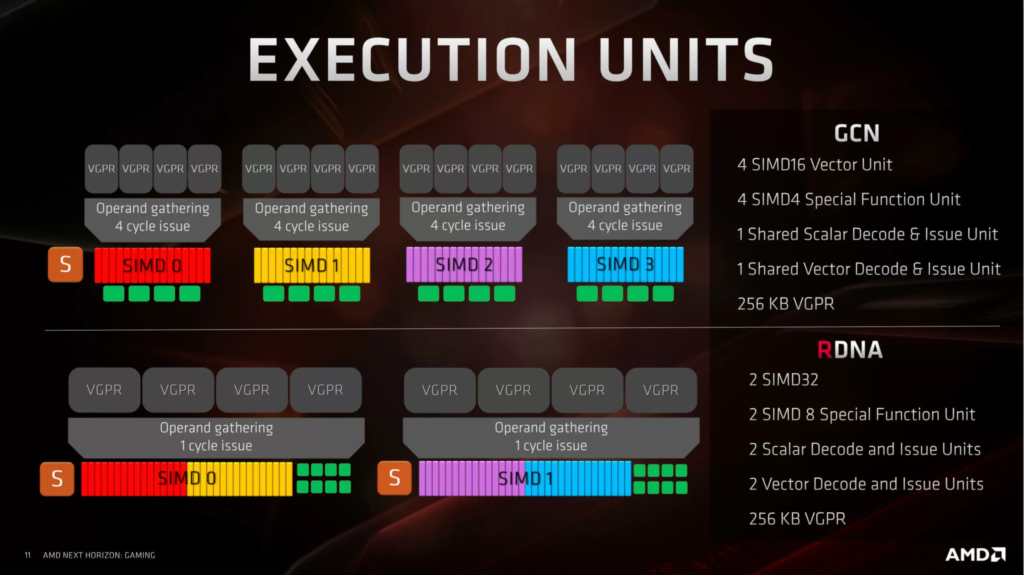

Navi e Turing trabalham de maneira semelhante, em que uma unidade central recebe todos os threads e, em seguida, começa a agendá-los e emiti-los. No chip AMD, essa função é desempenhada pelo processador de comandos gráficos ; na Nvidia, é o GigaThread Engine . Os threads são organizados de forma que aqueles com as mesmas instruções sejam agrupados, especificamente em uma coleção de 32 threads.

A AMD chama essa coleção de onda, enquanto a Nvidia a chama de dobra . Para Navi, uma unidade de computação pode lidar com 2 ondas (ou uma onda de 64 threads, mas isso leva o dobro do tempo), e em Turing, um multiprocessador de streaming funciona por meio de 4 warps. Em ambos os designs, as ondas / urdiduras são independentes, ou seja, não precisam que as outras terminem antes de começar.

Até agora, não há muita diferença entre Navi e Turing – ambos foram projetados para lidar com um grande número de threads, para renderizar e computar cargas de trabalho. Precisamos examinar quais processos esses threads para ver onde os dois gigantes da GPU se separam no design.

Uma diferença de execução – RDNA vs CUDA

A AMD e a Nvidia têm uma abordagem marcadamente diferente para suas unidades de sombreador unificadas, embora muito da terminologia usada pareça ser a mesma. As unidades de execução da Nvidia ( núcleos CUDA ) são escalares por natureza – o que significa que uma unidade realiza uma operação matemática em um componente de dados; por outro lado, as unidades da AMD ( Processadores de fluxo ) funcionam em vetores – uma operação em vários componentes de dados. Para operações escalares, eles têm uma única unidade dedicada.

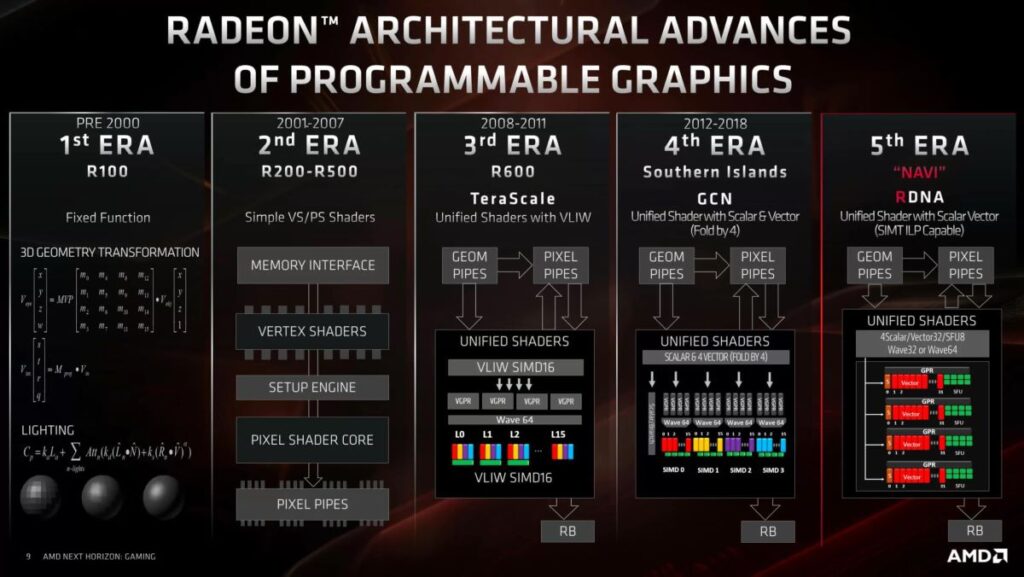

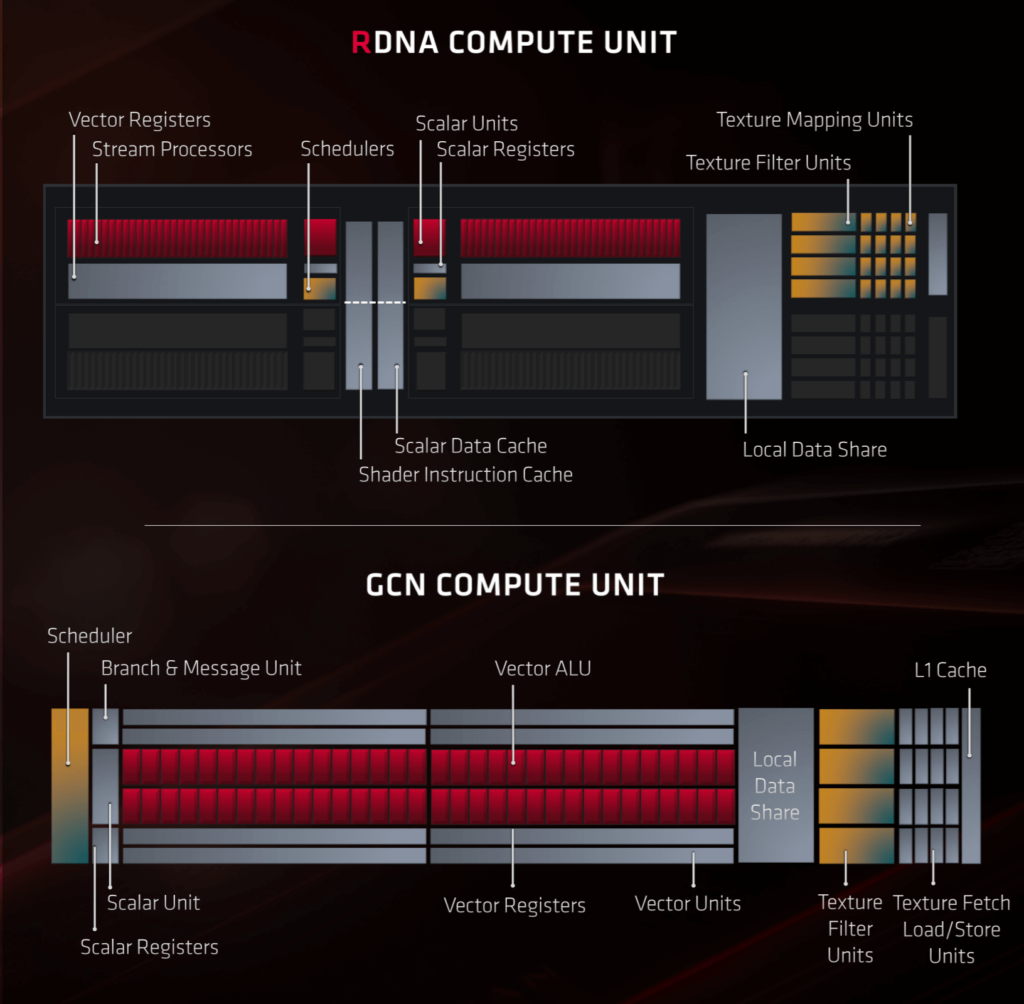

Antes de darmos uma olhada mais de perto nas unidades de execução, vamos examinar as mudanças da AMD nas unidades. Por 7 anos, as placas de vídeo Radeon seguiram uma arquitetura chamada Graphics Core Next (GCN). Cada novo chip revisou vários aspectos do design, mas todos eles foram fundamentalmente iguais.

A AMD forneceu uma (muito) breve história de sua arquitetura de GPU:

GCN foi uma evolução do TeraScale, um design que permitia que grandes ondas fossem processadas ao mesmo tempo. O principal problema com o TeraScale era que ele simplesmente não era muito amigável com os programadores e precisava de rotinas muito específicas para obter o melhor dele. O GCN corrigiu isso e forneceu uma plataforma muito mais acessível.

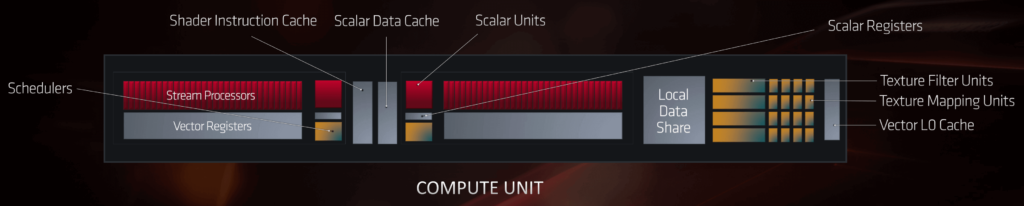

As UCs no Navi foram significativamente revisadas do GCN como parte do processo de aprimoramento da AMD. Cada CU contém dois conjuntos de:

- 32 SPs (IEE754 FP32 e ALUs de vetor INT32)

- 1 SFU

- 1 ALU escalar INT32

- 1 unidade de agendamento e despacho

Junto com eles, cada CU contém 4 unidades de textura. Existem outras unidades dentro, para lidar com a leitura / gravação de dados do cache, mas não são mostradas na imagem abaixo:

Comparado ao GCN, a configuração de um RDNA CU pode não parecer muito diferente, mas é como tudo foi organizado e organizado que é importante aqui. Para começar, cada conjunto de 32 SPs tem sua própria unidade de instrução dedicada, enquanto o GCN só tinha uma programação para 4 conjuntos de 16 SPs.

Esta é uma mudança importante, pois significa que uma onda de 32 encadeamentos pode ser emitida por ciclo de clock para cada conjunto de SPs. A arquitetura RDNA também permite que as unidades vetoriais manipulem ondas de 16 threads com o dobro da taxa e ondas de 64 threads com a metade da taxa, portanto, o código escrito para todas as placas gráficas Radeon anteriores ainda é suportado.

Para desenvolvedores de jogos, essas mudanças serão muito populares.

Para operações escalares, agora existem duas vezes mais unidades para lidar com isso; a única redução no número de componentes está na forma de SFUs – são unidades de funções especiais , que realizam operações matemáticas muito específicas, por exemplo, trigonométricas (seno, tangente), recíprocas (1 dividido por um número) e raízes quadradas. Há menos deles no RDNA em comparação com o GCN, mas agora eles podem operar em conjuntos de dados com o dobro do tamanho de antes.

Para desenvolvedores de jogos, essas mudanças serão muito populares. Placas de vídeo Radeon mais antigas tinham muito desempenho potencial, mas explorar isso era notoriamente difícil. Agora, a AMD deu um grande passo à frente na redução da latência nas instruções de processamento e também reteve recursos para permitir a compatibilidade com versões anteriores para todos os programas projetados para a arquitetura GCN.

Mas e quanto ao mercado de computação gráfica ou profissional? Essas mudanças são benéficas para eles também?

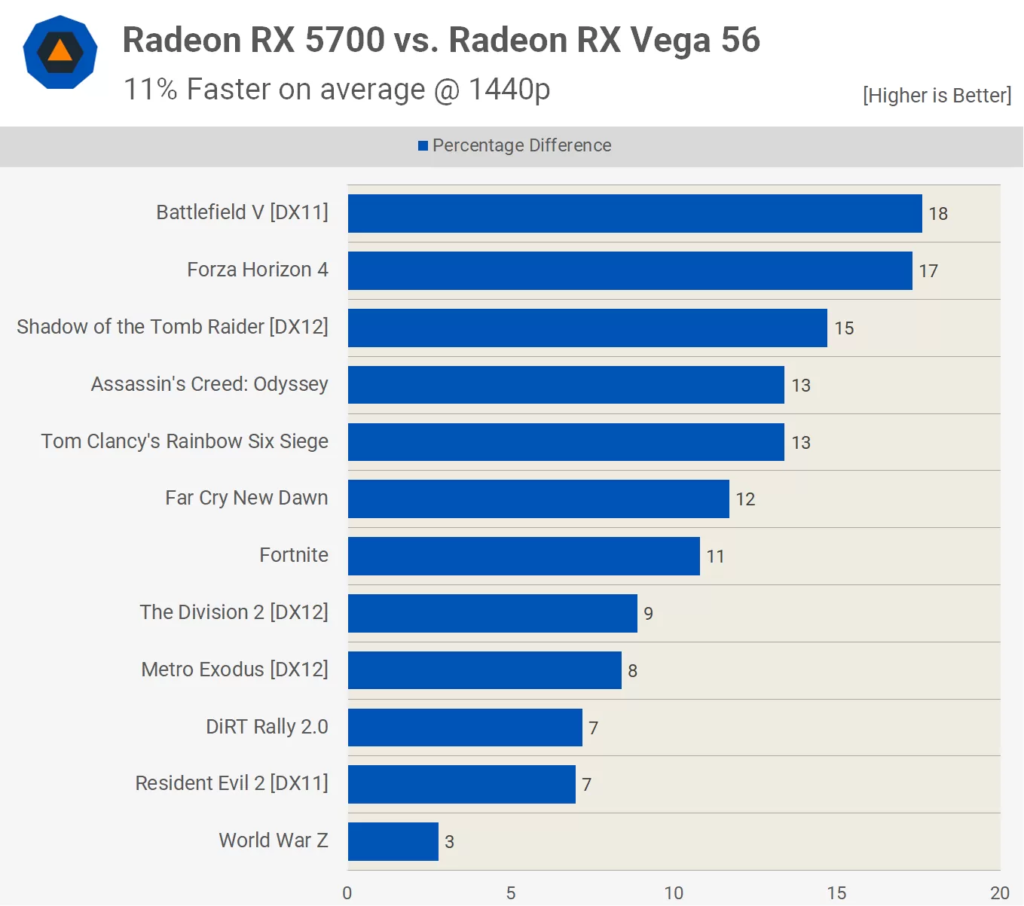

A resposta curta seria sim ( provavelmente ). Embora a versão atual do chip Navi, encontrada em similares ao Radeon RX 5700 XT, tenha menos processadores de fluxo que o design anterior do Vega, descobrimos que ele supera o desempenho de um Radeon RX Vega 56 da geração anterior com bastante facilidade:

Parte desse ganho de desempenho virá do RX 5700 XT com uma taxa de clock mais alta do que o RX Vega 56 (então ele pode gravar mais pixels por segundo na memória local), mas está abaixo do pico de desempenho de ponto flutuante e inteiro em até 15% ; e ainda assim, vimos o chip Navi superar o Vega em até 18%.

Programas de renderização profissional e cientistas que executam algoritmos complexos não vão exatamente passar por algumas rodadas do Battlefield V em seus trabalhos (bem, talvez …), mas se as operações escalares, vetoriais e matriciais feitas em um motor de jogo forem sendo processado mais rápido, isso deve se traduzir no mercado de computação.

No momento, não sabemos quais são os planos da AMD em relação ao mercado profissional – eles poderiam muito bem continuar com a arquitetura Vega e refinar o design para ajudar na fabricação, mas dadas as melhorias no Navi, faz sentido para a empresa mova tudo para a nova arquitetura.

O design da GPU da Nvidia passou por um caminho semelhante de evolução desde 2006, quando eles lançaram a série GeForce 8, embora com menos mudanças radicais do que a AMD. Esta GPU ostentava a arquitetura Tesla, uma das primeiras a usar uma abordagem de shader unificado para a arquitetura de execução. Abaixo, podemos ver as mudanças nos blocos SM do sucessor de Tesla (Fermi), até o predecessor de Turing (Volta):

Conforme mencionado anteriormente neste artigo, os núcleos CUDA são escalares . Eles podem realizar um float e uma instrução de inteiro por ciclo de clock em um componente de dados (observe, porém, que a própria instrução pode levar vários ciclos de clock para ser processada), mas as unidades de agendamento os organizam em grupos de tal forma que, para um programador, eles podem realizar operações vetoriais. A mudança mais significativa ao longo dos anos, além de simplesmente haver mais unidades, envolve como elas são organizadas e seccionadas.

No projeto do Kepler, o chip completo tinha 5 GPCs, com cada um abrigando três blocos SM; no momento em que Pascal apareceu, os GPCs foram divididos em seções discretas (TPCs) com dois SMs por TPC. Tal como acontece com o design Navi. essa fragmentação é importante, pois permite que a GPU geral seja utilizada da forma mais completa possível; vários grupos de instruções independentes podem ser processados em paralelo, aumentando o sombreamento e o desempenho de computação do processador.

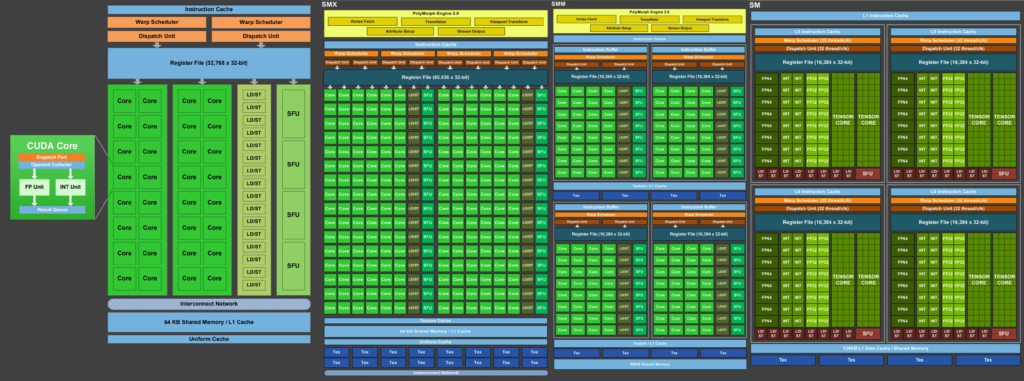

Vamos dar uma olhada no equivalente de Turing à unidade de computação RDNA:

Um SM contém 4 blocos de processamento, cada um contendo:

- 1 unidade de programação e despacho de instrução

- 16 ALUs escalares IEE754 FP32

- 16 ALUs escalares INT32

- 2 núcleos tensores

- 4 SFUs

- 4 unidades de carga / armazenamento (que lidam com leitura / gravação de cache)

Existem também 2 unidades FP64 por SM, mas a Nvidia não as mostra mais em seus diagramas de blocos, e cada SM abriga 4 unidades de textura (contendo endereçamento de texturização e sistemas de filtragem de texturização) e 1 núcleo RT (Ray Tracing).

As ALUs FP32 e INT32 podem funcionar simultaneamente e em paralelo. Este é um recurso importante porque, embora os mecanismos de renderização 3D exijam principalmente cálculos de ponto flutuante, ainda há um número razoável de operações inteiras simples (por exemplo, cálculos de endereço de dados) que precisam ser feitas.

Os Tensor Cores são ALUs especializadas que lidam com operações de matriz. As matrizes são matrizes de dados ‘quadradas’ e os núcleos do Tensor funcionam em matrizes 4 x 4. Eles são projetados para lidar com componentes de dados FP16, INT8 ou INT4 de tal forma que, em um ciclo de clock, até 64 operações de float FMA (fusão, multiplicação e adição) ocorrem. Esse tipo de cálculo é comumente usado nas chamadas redes neurais e inferência – não exatamente muito comum em jogos 3D, mas muito usado por empresas como o Facebook para seus algoritmos de análise de mídia social ou em carros que possuem sistemas de direção autônoma. O Navi também pode fazer cálculos de matriz, mas requer um grande número de SPs para fazê-lo; no sistema de Turing, as operações de matriz podem ser feitas enquanto os núcleos CUDA estão fazendo outra matemática.

O RT Core é outra unidade especial, exclusiva da arquitetura Turing, que executa algoritmos matemáticos muito específicos que são usados para o sistema de rastreamento de raios da Nvidia. Uma análise completa disso está além do escopo deste artigo, mas o RT Core é essencialmente dois sistemas que funcionam separadamente para o resto do SM, então ele ainda pode funcionar em vertex ou pixel shaders, enquanto o RT Core está ocupado fazendo cálculos para rastreamento de raio.

Em um nível fundamental, Navi e Turing têm unidades de execução que oferecem um conjunto de recursos razoavelmente semelhante (uma necessidade nascida da necessidade de cumprir os requisitos do Direct3D, OpenGL, etc.), mas …

Em um nível fundamental, Navi e Turing têm unidades de execução que oferecem um conjunto de recursos razoavelmente semelhante (uma necessidade nascida da necessidade de cumprir os requisitos do Direct3D, OpenGL, etc.), mas eles têm uma abordagem muito diferente de como esses recursos são processado. Quanto a qual design é melhor, tudo se resume a como eles são usados: um programa que gera muitos threads realizando cálculos vetoriais FP32 e pouco mais parece favorecer o Navi, enquanto um programa com uma variedade de cálculos inteiros, flutuantes, escalares e vetoriais favoreceria a flexibilidade de Turing e assim por diante.

A Hierarquia de Memória

As GPUs modernas são processadores de streaming, ou seja, são projetadas para executar um conjunto de operações em cada elemento de um fluxo de dados. Isso os torna menos flexíveis do que uma CPU de uso geral e também requer que a hierarquia de memória do chip seja otimizada para obter dados e instruções para as ALUs o mais rápido possível e em tantos fluxos quanto possível. Isso significa que as GPUs terão menos cache do que uma CPU, pois mais do chip precisa ser dedicado ao acesso ao cache, em vez da quantidade de cache em si.

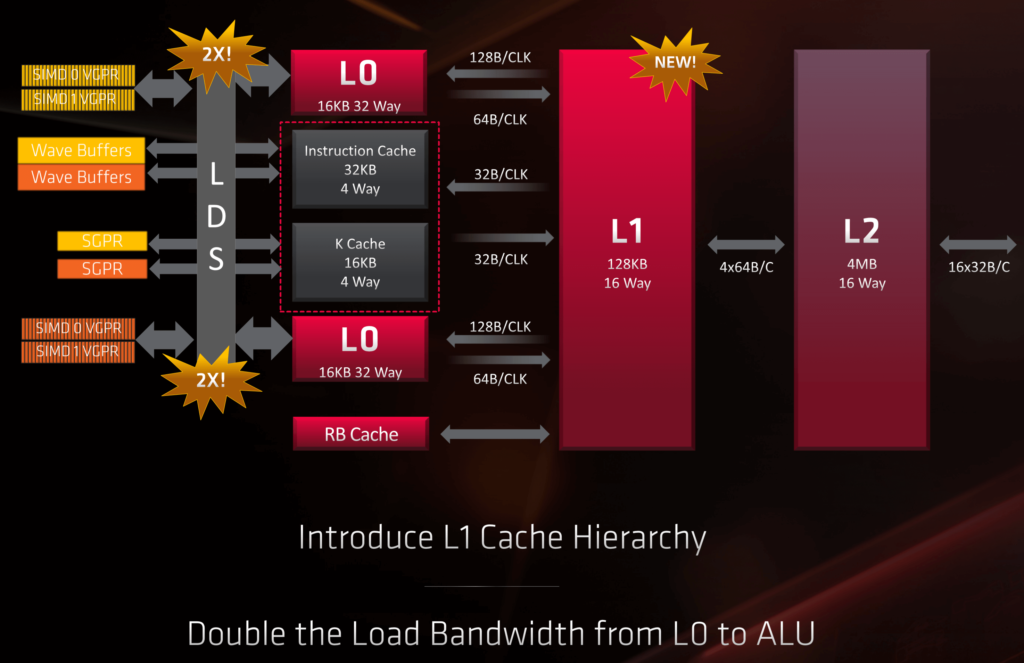

Tanto a AMD quanto a Nvidia recorrem ao uso de vários níveis de cache dentro dos chips, então vamos dar uma olhada no que o Navi traz primeiro.

Começando no nível mais baixo na hierarquia, os dois blocos de Processadores de Fluxo utilizam um total de 256 kiB de registradores de uso geral de vetor (geralmente chamado de arquivo de registro ), que é a mesma quantidade que em Vega, mas isso foi em 4 blocos SP; ficar sem registros ao tentar processar um grande número de threads realmente prejudica o desempenho, então isso é definitivamente uma “coisa boa”. A AMD também aumentou muito o arquivo de registro escalar. Onde antes era de apenas 4 kiB, agora é de 32 kiB por unidade escalar.

Duas unidades de computação compartilham um cache L0 de instrução de 32 kiB e um cache de dados escalares de 16 kiB, mas cada CU obtém seu próprio cache L0 vetorial de 32 kiB; conectar toda essa memória às ALUs é um compartilhamento de dados local de 128 kiB.

No Navi, dois Compute Engines formam um Processador de grupo de trabalho e cinco deles formam um Asynchronous Compute Engine (ACE). Cada ACE tem acesso aos seus próprios 128 kiB de cache L1 e toda a GPU é ainda suportada por 4 MiB de cache L2, que está interconectado aos caches L1 e outras seções do processador.

Esta é quase certamente uma forma da arquitetura de interconexão Infinity Fabric proprietária da AMD, já que o sistema é definitivamente empregado para lidar com 16 controladores de memória GDDR6. Para maximizar a largura de banda da memória, o Navi também emprega compactação de cores sem perdas entre L1, L2 e a memória GDDR6 local.

Novamente, tudo isso é bem-vindo, especialmente quando comparado aos chips AMD anteriores, que não tinham cache de baixo nível suficiente para o número de unidades de shader que continham. Em resumo, mais cache equivale a mais largura de banda interna, menos instruções paralisadas (porque eles estão tendo que buscar dados da memória mais longe) e assim por diante. E isso simplesmente significa melhor desempenho.

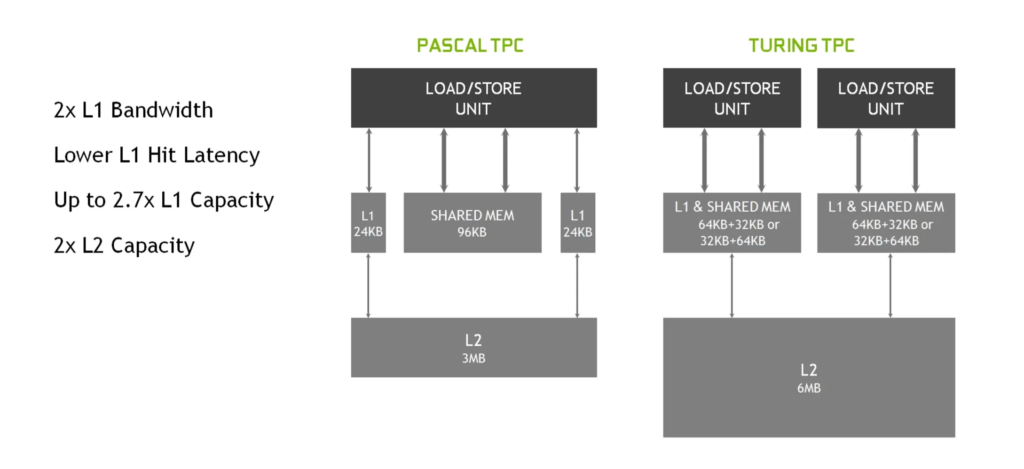

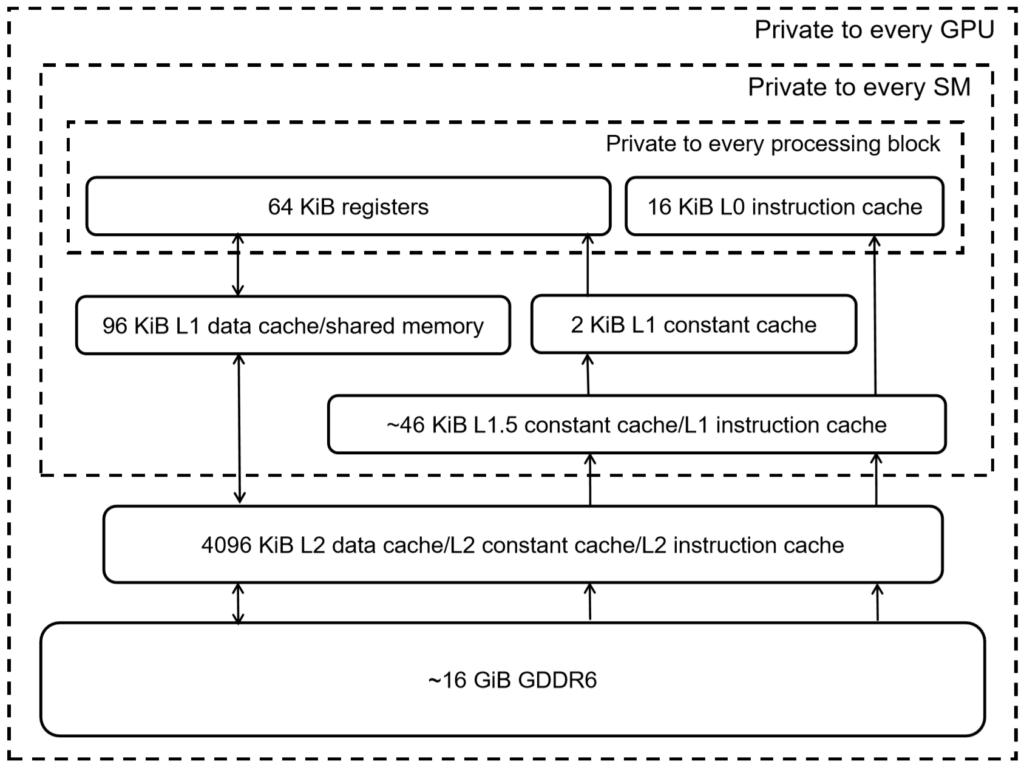

Sobre a hierarquia de Turing, deve-se dizer que a Nvidia é tímida quando se trata de fornecer informações detalhadas nesta área. Anteriormente neste artigo, vimos que cada SM foi dividido em 4 blocos de processamento – cada um deles tem um arquivo de registro de 64 kiB, que é menor do que o encontrado no Navi, mas não se esqueça de que as ALUs de Turing são escalares, não vetoriais, unidades.

Em seguida vem 96 kiB de memória compartilhada, para cada SM, que pode ser empregado como 64 kiB de cache de dados L1 e 32 kiB de cache de textura ou espaço de registro extra. No ‘modo de computação’, a memória compartilhada pode ser particionada de maneira diferente, como memória compartilhada de 32 kiB e cache L1 de 64 kiB, mas isso sempre é feito como uma divisão de 64 + 32.

A falta de detalhes sobre o sistema de memória Turning nos deixou querendo mais, então procuramos uma equipe de pesquisa de GPU, trabalhando na Citadel Enterprise Americas. Recentemente, eles lançaram dois artigos, analisando os melhores aspectos das arquiteturas Volta e Turing; a imagem acima é o detalhamento da hierarquia de memória no chip TU104 (o TU102 completo possui 6144 kiB de cache L2).

A equipe confirmou que a taxa de transferência do cache L1 é de 64 bits por ciclo e observou que, em testes, a eficiência do cache L1 de Turing é a melhor de todas as GPUs da Nvidia. Isso está no mesmo nível do Navi, embora o chip da AMD tenha uma taxa de leitura mais alta para o Armazenamento de Dados Local, mas uma taxa mais baixa para os caches de instrução / constantes.

Ambas as GPUs usam GDDR6 para a memória local – esta é a versão mais recente do Graphics DDR SDRAM – e ambas usam conexões de 32 bits para os módulos de memória, então uma Radeon RX 5700 XT tem 8 chips de memória, dando uma largura de banda de pico de 256 GiB / se 8 GiB de espaço. Uma GeForce RTX 2080 Ti com um chip TU102 funciona com 11 desses módulos para 352 GiB / s de largura de banda e 11 GiB de armazenamento.

Os documentos da AMD podem parecer confusos às vezes: no primeiro diagrama de blocos que vimos do Navi, ele mostra quatro controladores de memória de 64 bits, enquanto uma imagem posterior sugere que há 16 controladores. Dado que empresas como a Samsung oferecem apenas módulos de memória GDDR6 de 32 bits, parece que a segunda imagem apenas indica quantas conexões existem entre o sistema Infinity Fabric e os controladores de memória. Provavelmente existem apenas 4 controladores de memória e cada um lida com dois módulos.

Portanto, no geral, não parece haver uma enorme diferença entre Navi e Turing no que diz respeito a seus caches e memória local. Navi tem um pouco mais do que Turing mais perto do lado da execução das coisas, com maiores instruções / constantes e caches L1, mas ambos estão cheios de coisas, ambos usam compressão de cores sempre que possível, e ambos têm muitos dados de GPU dedicados espaço para maximizar o acesso à memória e largura de banda.

Triângulos, texturas e pixels

Quinze anos atrás, os fabricantes de GPU se preocupavam muito com quantos triângulos seus chips podiam processar, o número de elementos de textura que podiam ser filtrados a cada ciclo e a capacidade das unidades de saída de renderização (ROPs). Esses aspectos ainda são importantes hoje, mas como as tecnologias de renderização 3D exigem muito mais desempenho de computação do que nunca, o foco está muito mais no lado da execução das coisas.

No entanto, as unidades de textura e ROPs ainda valem a pena investigar, apenas para notar que não há diferença imediatamente perceptível entre Navi e Turing nessas áreas. Em ambas as arquiteturas, as unidades de textura podem endereçar e buscar 4 elementos de textura, filtrá-los bilinearmente em um elemento e gravá-los no cache em um ciclo de clock (desconsiderando quaisquer ciclos de clock adicionais tomados para buscar os dados da memória local).

O arranjo dos ROP / RBs é um pouco diferente entre Navi e Turing, mas não muito: o chip AMD tem 4 RBs por ACE e cada um pode produzir 4 pixels combinados por ciclo de clock; em Turing, cada GPC ostenta dois RBs, com cada um fornecendo 8 pixels por clock. A contagem de ROP de uma GPU é realmente uma medida dessa taxa de saída de pixel, então um chip Navi completo fornece 64 pixels por clock, e o TU102 completo fornece 96 (mas não se esqueça que é um chip muito maior).

No lado triangular das coisas, há menos informações imediatas. O que sabemos é que o Navi ainda produz no máximo 4 primitivos por ciclo de clock (1 por ACE), mas não há nada ainda sobre se a AMD resolveu ou não o problema referente aos seus primitivos Shaders.

Esse era um recurso muito elogiado do Vega, permitindo que os programadores tivessem muito mais controle sobre os primitivos, de modo que pudesse aumentar potencialmente o rendimento do primitivo em um fator de 4. No entanto, a funcionalidade foi removida dos drivers em algum ponto não muito depois do produto lançamento, e tem permanecido dormente desde então.

Enquanto ainda esperamos por mais informações sobre Navi, não seria sensato especular mais. Turing também processa 1 primitivo por clock por GPC (até 6 para a GPU TU102 completa) nos Raster Engines, mas também oferece algo chamado Mesh Shaders, que oferece o mesmo tipo de funcionalidade dos Primitive Shaders da AMD; não é um conjunto de recursos do Direct3D, OpenGL ou Vulkan, mas pode ser usado por meio de extensões de API.

Isso parece estar dando a Turing uma vantagem sobre Navi, em termos de manipulação de triângulos e primitivos, mas não há informações suficientes de domínio público neste momento para ter certeza.

Não se trata apenas das unidades de execução

Existem outros aspectos de Navi e Turing que valem a pena comparar. Para começar, ambas as GPUs têm mecanismos de exibição e mídia altamente desenvolvidos. O primeiro lida com a saída para o monitor, o último codifica e decodifica fluxos de vídeo.

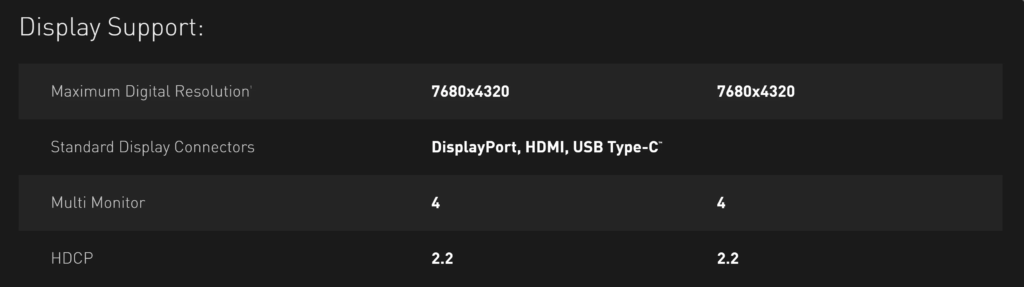

Como você esperaria de um novo design de GPU 2019, o mecanismo de exibição do Navi oferece resoluções muito altas, com altas taxas de atualização e oferece suporte a HDR. O Display Stream Compression (DSC) é um algoritmo de compressão rápida com perdas que permite que resoluções como 4K + em taxas de atualização de mais de 60 Hz sejam transmitidas em uma conexão DisplayPort 1.4; felizmente, a degradação da qualidade da imagem é muito pequena, quase ao ponto de considerar o DSC virtualmente sem perdas.

Turing também suporta DisplayPort com conexões DSC, embora a combinação de alta resolução e taxa de atualização suportada seja ligeiramente melhor do que no Navi: 4K HDR está a 144 Hz – mas o resto é o mesmo.

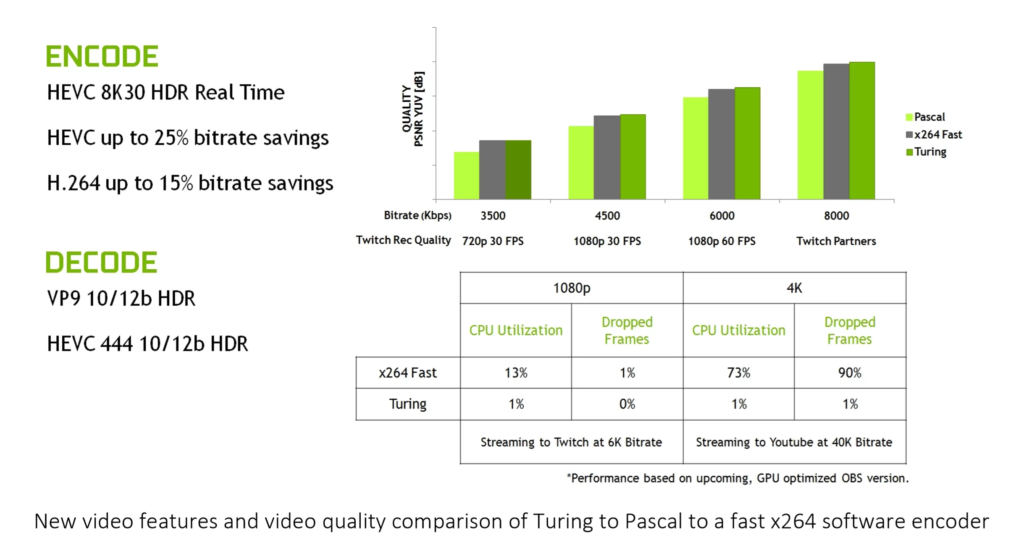

O mecanismo de mídia da Navi é tão moderno quanto seu mecanismo de exibição, oferecendo suporte para Codificação de Vídeo Avançada (H.264) e Codificação de Vídeo de Alta Eficiência (H.265), novamente em altas resoluções e altas taxas de bits.

O mecanismo de vídeo de Turing é quase o mesmo do Navi, mas o suporte à codificação 8K30 HDR pode inclinar a balança a favor de Turing para algumas pessoas.

Existem outros aspectos para comparar (interface PCI Express 4.0 da Navi ou NV Link de Turing, por exemplo), mas eles são realmente apenas partes menores da arquitetura geral, não importa o quanto eles sejam vestidos e comercializados. Isso ocorre simplesmente porque, para a grande maioria dos usuários em potencial, esses recursos exclusivos não farão diferença.

AMD Navi ou Nvidia Turing: Comparando like-for-like

Este artigo é uma observação do projeto arquitetônico, dos recursos e da funcionalidade, mas ter uma comparação direta de desempenho seria uma boa maneira de concluir essa análise. No entanto, combinar o chip Navi em uma Radeon RX 5700 XT com o processador Turing TU102 em uma GeForce RTX 2080 Ti, por exemplo, seria nitidamente injusto, dado que o último tem quase o dobro do número de unidades de sombreador unificadas que o anterior. No entanto, existe uma versão do chip Turing que pode ser usada para comparação e é o da GeForce RTX 2070 Super.

| Radeon RX 5700 XT | GeForce RTX 2070 Super | |

| GPU | Arquitetura | Navi 10 | RDNA | TU104 | Turing |

| Processar | 7 nm TSMC | 12 nm TSMC |

| Área da matriz (mm 2 ) | 251 | 545 |

| Transistores (bilhões) | 10,3 | 13,6 |

| Perfil de bloco | 2 SE | 4 ACE | 40 CU | 5 GPC | 20 TPC | 40 SM |

| Núcleos de shader unificados | 2560 SP | 2560 CUDA |

| TMUs | 160 | 160 |

| ROPs | 64 | 64 |

| Relógio base | 1605 MHz | 1605 MHz |

| Relógio de jogo | 1755 MHz | N / D |

| Relógio de impulso | 1905 MHz | 1770 MHz |

| Memória | GDDR6 de 8 GB de 256 bits | GDDR6 de 8 GB de 256 bits |

| Largura de banda de memória | 448 GBps | 448 GBps |

| Energia de Design Térmico (TDP) | 225 W | 215 W |

É importante notar que o RTX 2070 Super não é um chip TU104 ‘completo’ (um dos GPCs está desabilitado), então nem todos os transistores 13.6 estão ativos, o que significa que os chips são praticamente os mesmos em termos de contagem de transistores. Pelo valor de face, as duas GPUs parecem muito semelhantes, especialmente se você considerar apenas o número de unidades de sombreador, TMUs, ROPs e os sistemas de memória principais.

No processador Nvidia, um SM pode lidar com 32 warps simultâneos e com cada warp consistindo em 32 threads, uma GeForce RTX 2070 Super totalmente carregada pode trabalhar em 40.960 threads em todo o chip; para Navi, uma CU pode levar até 16 ondas por SIMD32 ALU, com cada onda sendo 32 encadeamentos.

Portanto, a Radeon RX 5700 XT também pode ser embalada com até 40.960 threads. Isso parece torná-los exatamente iguais aqui, mas dada a forma como os CU / SMs são organizados de maneira diferente e a vantagem da Nvidia com o processamento simultâneo de INT e FP, o resultado final dependerá muito do código que está sendo executado.

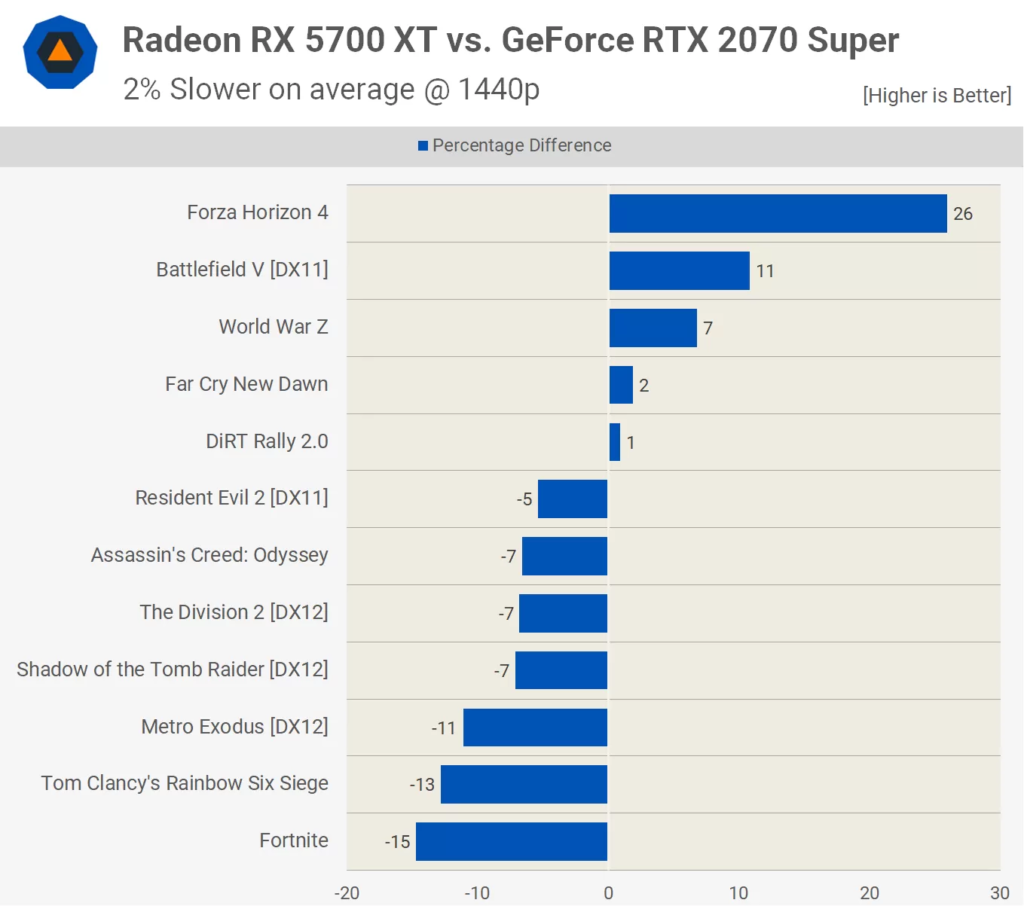

Isso terá um impacto no desempenho de vários jogos, porque o código de um mecanismo 3D favorecerá uma estrutura melhor do que a outra, dependendo de quais tipos de instruções são enviados rotineiramente para a GPU. Isso ficou evidente quando testamos as duas placas gráficas :

Todos os jogos usados no teste foram programados para a arquitetura GCN da AMD, seja diretamente para PCs equipados com Radeon ou através de GPUs GCN encontrados em jogos como o PlayStation 4 ou Xbox One. É possível que alguns dos lançados mais recentemente pudessem ter se preparado para as mudanças de RDNA, mas as diferenças vistas nos resultados do benchmark são mais prováveis devido aos motores de renderização e a maneira como as instruções e dados estão sendo tratados.

Então, o que tudo isso significa? Uma arquitetura é realmente melhor que a outra? Turing certamente oferece mais capacidade do que o Navi graças aos seus núcleos Tensor e RT, mas o último certamente compete em termos de desempenho de renderização 3D. As diferenças vistas em uma amostra de 12 jogos não são conclusivas o suficiente para fazer um julgamento definitivo.

E isso é uma boa notícia para nós.

AMD Navi ou Nvidia Turing: Palavras Finais

Os planos da AMD para a Navi foram anunciados em 2016 e, embora não tenham falado muito naquela época, o objetivo era o lançamento em 2018. Quando essa data chegou e passou, o roteiro mudou para 2019, mas estava claro que o Navi seria fabricado em um nó de processo de 7 nm e o design se concentraria em melhorar o desempenho.

Esse certamente foi o caso e, como vimos neste artigo, a AMD fez mudanças arquitetônicas para permitir que competisse com ofertas equivalentes da Nvidia. O novo design beneficia mais do que apenas os usuários de PC, pois sabemos que a Sony e a Microsoft vão usar uma variante do chip no próximo PlayStation 5 e no próximo Xbox.

Se você voltar para o início deste artigo e olhar novamente para o design estrutural dos motores Shader, bem como o tamanho geral da matriz e a contagem de transistores, há claramente espaço para um chip ‘grande Navi’ entrar em um top- placa gráfica final; A AMD praticamente confirmou que isso faz parte de seus planos atuais, além de buscar um refinamento da arquitetura e do processo de fabricação nos próximos dois anos.

Mas e quanto à Nvidia, quais são seus planos para Turing e seu sucessor? Surpreendentemente, muito pouco foi confirmado pela empresa. Em 2014, a Nvidia atualizou seu roteiro de GPU para agendar a arquitetura Pascal para um lançamento em 2016 (e atingiu essa meta). Em 2017, eles anunciaram o Tesla V100, usando sua arquitetura Volta, e foi esse design que gerou Turing em 2018.

Desde então, as coisas têm estado bastante calmas, e tivemos que confiar em rumores e fragmentos de notícias, que geralmente dizem a mesma coisa: a próxima arquitetura da Nvidia se chamará Ampere, será fabricada pela Samsung usando seu nó de processo de 7 nm, e está planejado para 2020. Fora isso, não há mais nada para continuar. É altamente improvável que o novo chip rompa a tradição com o foco em unidades de execução escalar, nem é provável que elimine aspectos como os núcleos do Tensor, pois isso causaria problemas de compatibilidade retroativa significativos.

Podemos fazer algumas suposições razoáveis sobre como será a próxima GPU da Nvidia. A empresa investiu uma quantidade notável de tempo e dinheiro no rastreamento de raios , e o suporte para ele em jogos só vai aumentar; portanto, podemos esperar ver uma melhoria com os núcleos RT, seja em termos de capacidade ou número por SM. Se assumirmos que o boato sobre o uso de um nó de processo de 7 nm é verdadeiro, então a Nvidia provavelmente terá como objetivo uma redução de energia em vez de um aumento total da velocidade do clock, para que possa aumentar o número de GPCs. Também é possível que 7 nm seja ignorado e a Nvidia vá direto para 5 nm para ganhar uma vantagem sobre a AMD.

E parece que a AMD e a Nvidia enfrentarão uma nova competição no mercado de placas de vídeo discretas da Intel, como sabemos que eles planejam entrar novamente neste setor, após um hiato de 20 anos. Se este novo produto (atualmente denominado Xe) será capaz de competir no mesmo nível que Navi e Turing ainda está para ser visto.

Enquanto isso, a Intel se manteve viva no mercado de GPU ao longo dessas 2 décadas, fazendo gráficos integrados para suas CPUs. A mais recente GPU da Intel, a Gen 11 , é mais parecida com a arquitetura da AMD do que com a da Nvidia, pois usa ALUs vetoriais que podem processar dados FP32 e INT32, mas não sabemos se as novas placas de vídeo serão uma evolução direta deste design.

O certo é que os próximos anos serão muito interessantes, enquanto os três gigantes das estruturas de silício continuarem batalhando por nossas carteiras. Novos designs e arquiteturas de GPU vão aumentar a contagem de transistores, tamanhos de cache e capacidades de sombreador.

Navi e RDNA são os mais novos de todos e mostraram que cada passo em frente, por menor que seja, pode fazer uma enorme diferença.

Agora você tem um pouco mais de conhecimento para escolher entre AMD Navi ou Nvidia Turing.